#### Introduction

## Introduction to Ic technology :-

Gi. Venkata Hanuman

It is an electronic assembly maintain such away that all components of the circuit are fabricated on a single container called chip (or) IC.

\* The technique to Increase no. of devices per chip is called Level of Integration.

It mainly consists of

- 1. SS I → Small Scale Integration

- 2. MSI -> medium scale Integration

- 3. LSI -> Large scale Integration

- 4. VLSI -> Very large scale Integration

- 5. ULSI -> Ultra large scale Integration

| -A) •                 | <b>51.</b> 1000 -                       |        |      | 9                                     |

|-----------------------|-----------------------------------------|--------|------|---------------------------------------|

| Type of Ic technology |                                         | Device | Year | Applications                          |

|                       |                                         |        | 1960 | Grates, OP-AMPS                       |

| 7                     | 581 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 1-100  |      |                                       |

|                       | msi ····                                | ioc-IK | 1965 | Registers, filters                    |

|                       | MIST                                    | IK-loK | 1970 | AlD , DIA , micro Processors          |

| ?                     | LSI                                     |        |      | · · · · · · · · · · · · · · · · · · · |

|                       | VLSI                                    | >lok   | 1975 | memories, DSP kits                    |

|                       | VLSI                                    |        |      |                                       |

Advantages of Ic's :-

\* Low Power consumption

\* Faisy replacement

- \* High speed of operation

- \* small in size

- \* Reduce cost

- \* High reliability

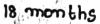

moore states that the transistor count double for ever

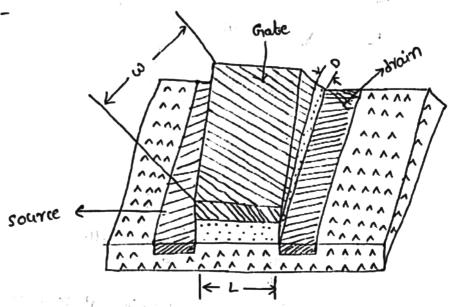

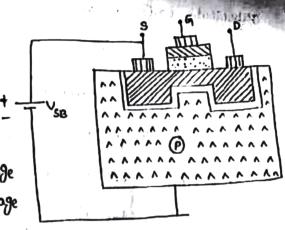

metal oxide Semi conductor (mos transistor):-

Principle:- A voltage is applied to the gate terminal, it controls the current in a conducting channel between source and drain.

Ex:-Innmos, the majority carriers are electrons.

Atve voltage applied on gate write substrate it enhances no of electrons in the channel and Increases the conductivity of channel.

For Gate Voltage is less than threshold Voltage value, the channel is cut-off, thus causing a very low drain-to-source current.

Threshold voltage (VE):- The voltage at which a mos device begins to conduct (turn on).

# key representations

nimas diramsistor:

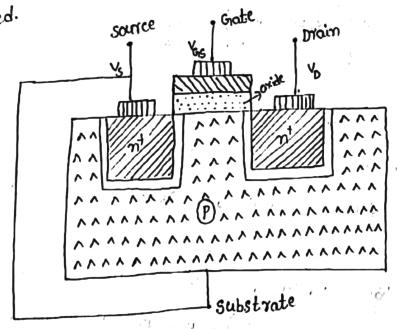

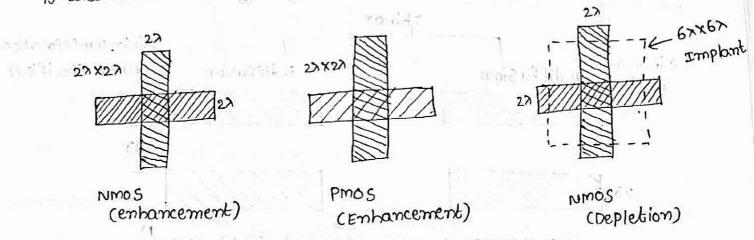

1. Nmos enhancement mode transistor :-

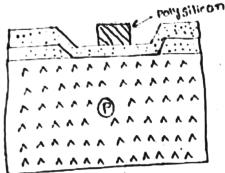

It consists of moderately doted. P-type silicon substrate into which two heavily doped not regions, namely source and drain are diffused.

- Between Source and drain there is a narrow region of P-type

Substrate called channel which is covered at the top with Sion (oxide) layer

over the Sion layer, polysilican gate is deposited over the regions

between drain and source.

- hence it is not conducting.

field is established between Jake and substrate.

conditions are reveired

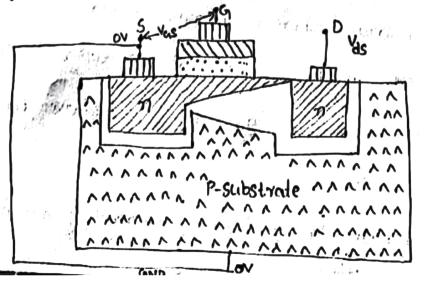

condition -1: Yes = 0

Inthis condition, a channel between drain and source is established but no current is flowing between source and drain he 45=0

condition -a :- Ys < ys - Yt

when is is applied between drain and source, current starts floring through channel.

\* The resistance of channel varies along its length this results in IR drop along the channel. The Voltage is maximum at source end.

The effective gate voltage  $y = ys - v_b$  as no current flows when 95 < Ve As long as (Ygs-VE) > Yds, the channel will be Inverted at drain end.

In this condition, device is in non-saturated region of operation.

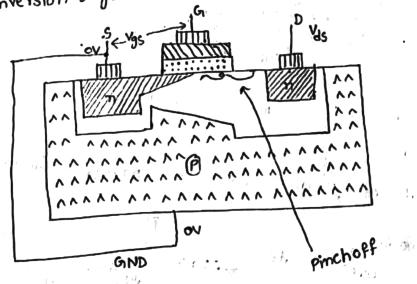

If is is Increased to greater than (Vgs-Vt), in such condition IR drop = Vgs-Ve takes place over less than whole length of channel. so, at drain terminal Insufficient electric field available to give rise to an Inversion layer create a channel. The channel is Pinchoff.

diffusion current completes the path from \* In this condition,

\* The device operated in Saturation region. The device behaves a con source for Increase of 4s above 4s = 9s-Vt.

when transistor operated in depletion made, even when yes

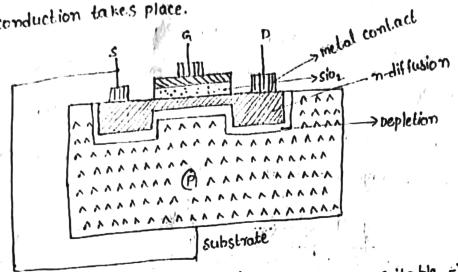

- Applying we voltage to the gate, current flows in a n-type transist and conduction takes place.

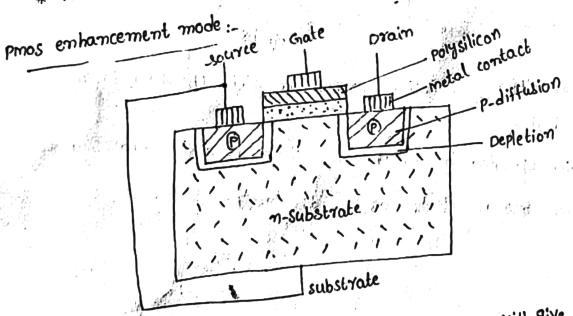

- \* similarly, the voltage to the gate, current flows in a p-type transistor and conduction takes place.

\* The channel width can be controlled by applying suitable -ve voltage to

\* variation in gate voltage allow control of current between source & drain.

\* applying -ve voltage between gate and source will give rise to formation of P-type channel between source and drain.

of drain is made we wireto source current can flow through chann

\* Here the current is carried by holes.

The hole mobility (up) compared to electron mobility (un) is 2.5 times less.

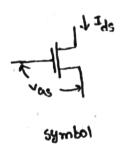

commonly used symbols for Nmos and Pmos:

nmos Enhancement

nmos pepletion

Pmos Enhancement

Nmos Fabrication Process :-

Step1: wafer pre paration:

Let us consider a single peace of silicon material and it is moderately doped with P-substrate. The water diameter is 75 to 150mm and thick ness is oumm. The p-substrate is boran.

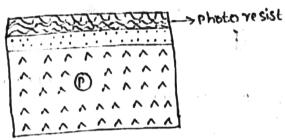

Steps: - oxidation: To Protect the surface, a layer of silicon dioxide (sio2) is grown over the surface. The thickness of sion is typically 14m.

This layer act as a barrier to dopants during processing.

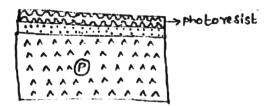

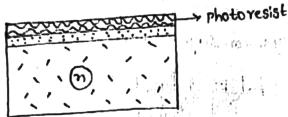

Step 3: - photo resist :-

. 51

The surface is now covered with photo resist which is deposited

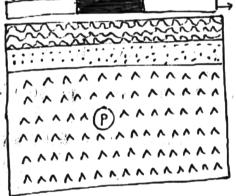

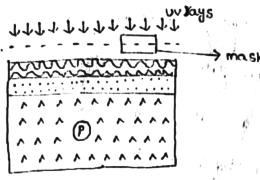

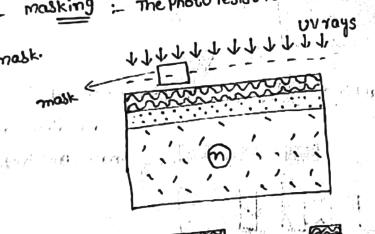

step4:- masking:- The Photo resist layer is exposed to UV light through a mask.

The mask corresponds to regions into which diffusion is to take place with transistor channels.

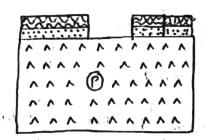

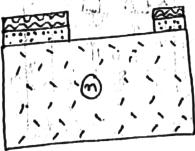

Step5:- Etching:- The regions are then etched to gether so that the wafer surface is exposed in window defined by mask.

BROWN TO BE TO SEE

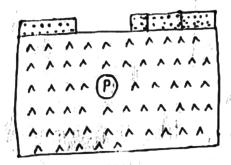

Remaining photoresist is removed and a thin layer of sion is deposited on top of this to form the gate structure.

The Polysilican layer consists of heavily doped Polysilican deposition (CVD).

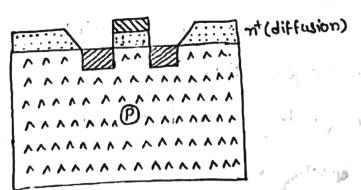

slep7: nt diffusion:

The thin oxide is removed to expose areas into which n-type Impurities are to be diffused from source and drain.

\* Diffusion is achieved by heating the wafer to high temperature and passing gas containing the desired n-type Impurity over the surface

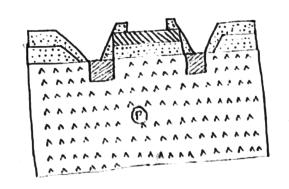

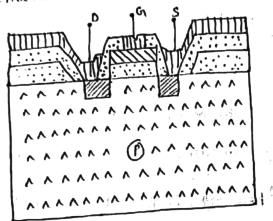

step 8 contact cuts (holes):- Thick silicon dioxide (sio2) is grown and then masked with photo resist and then etched to expose specific areas of polysilicon gate, drain and source areas where connections are made.

Step9 :- metallization:

The metal (n.l.) is deposited over its surface to a thickness typically of 121m. This metal dayer is then masked and etched to form the reactived Interconnection pattern.

regular governor by the same

cmos Fabrication process:

cmos can be obtained by Integrating both the Nmos and

pmos devices on the same chip.

The cross can be fabricated using different processes such as

- is N-well Process

- i) P-well process

- iii) Twintub Process

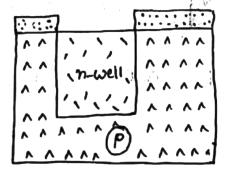

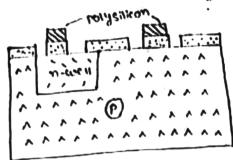

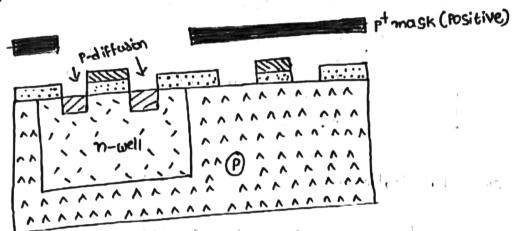

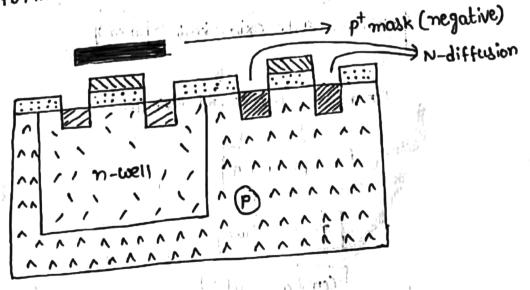

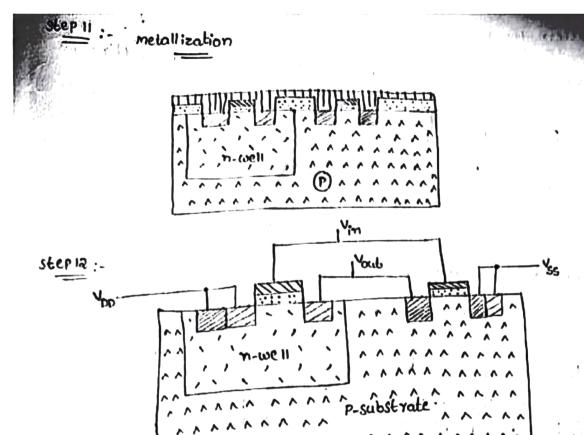

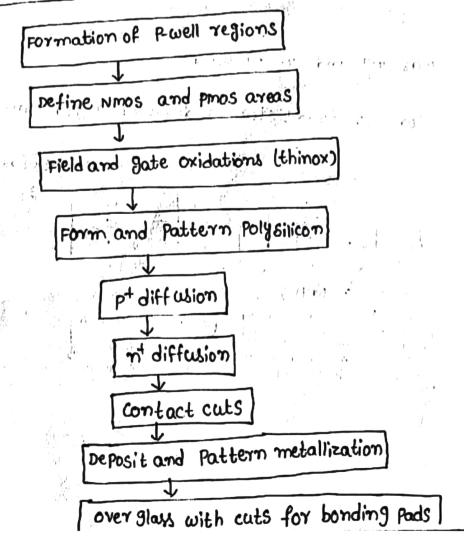

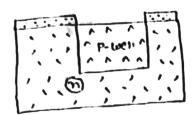

cmos fabrication :. motor steps: Formation of nevel Define Nmos and Pmos areas rield and gate exidations (thirox) Form and Patilern Polysilicon pt diffusion of diffusion contact cuts Deposit and Pattern metallization overglass with cuts for bonding pads consider a P-type substrate in mile step2; oxidation The entire Surface is coated with Sion layer

Step3:- photoresist: - Now, photoresist is contined entire surface.

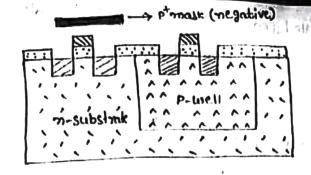

stepy:- masking the photo resist is exposed to uv stays through the N-well mask.

steps: Etching

step6: Removal of Photoresist:

then the entire layer of photoresist is stripped off.

Step7:- Formation of N-well:- By using diffusion process N-well is formed

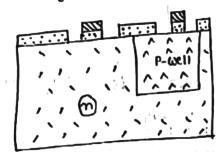

pattern the Polysilleon layer which is deposited after thinoxide

step 9:- pt diffusion and masking

P-diffusion regions are diffused to form the terimals of the

pmos.

step 10 :- masking and nt diffusion:-

To form n-transistor, n-diffusion regions are used.

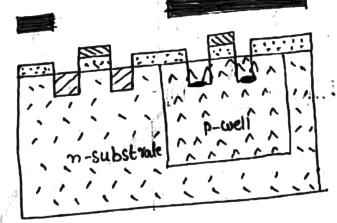

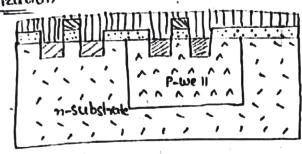

# a. P-well cmos fabrication;

pakir

ox idation

The embire surface is coated with sing layer

photoresist

Now the entire surface covered with a photoresist

stepy: masking: The photoresist is exposed to UV rays through the p-well

Step6 Removal of Photoresist:

The Photo resist can be removed using of hydroflouring acid. Then the entire layer of photoresist is stripped off.

slep 7: - Formation of P-well: "Busing diffusion process P-well is formed

steps:- Pattern the polysilkon layer;

The Polysilicon layer which is deposited after thin oxide.

stepig:- pt diffusion and masking: To form p-transister, p-diffusion regio

step ID: - masking and midiffusion:-

To form n-transistor, n-diffusion regions are used.

I was a series of the second of the second

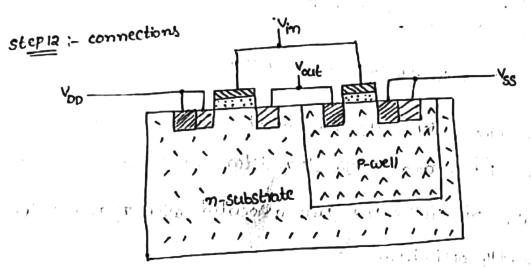

Stepn: \_ metallization

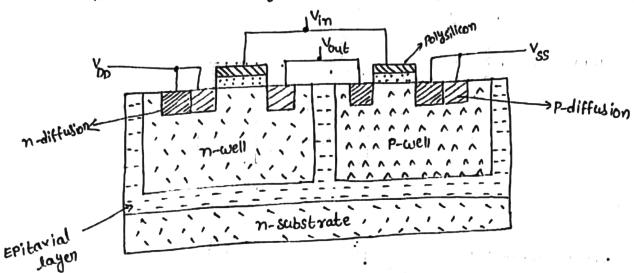

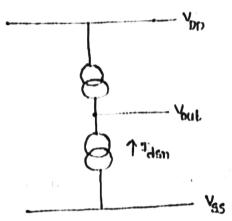

Twin tub process : The day many

- A twin-tub Process is a logical extension of P-well and n-well approaches.

- The process starts with a substrate of high resistivity n-type material and then both p-well and n-well regions are created.

- with this process it is possible to preserve the performance of n-transistors without compromising p-transistors

control to the tipes of an indicate the theorem later

as the twin-tub process allows separate optimization of pand in transistors.

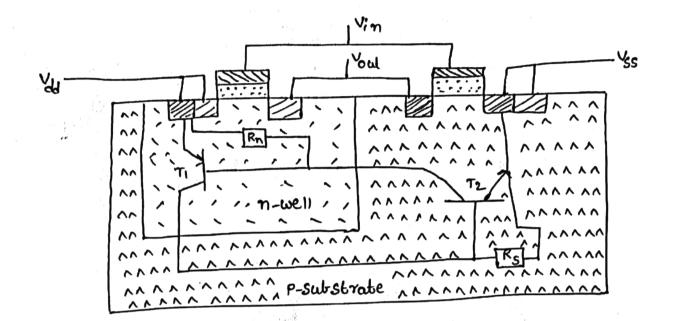

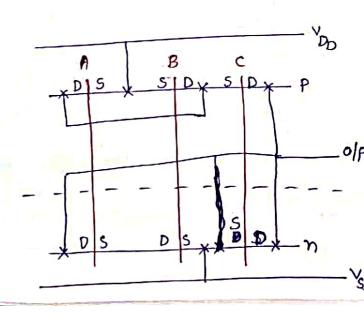

An Inverter arrangement of twin-tub as shown in fig.

Fig: Twin-tub Inverter structure.

The twin-tub cmos technology provides the basic for Separate optimization of p-type and n-type transistor making it possible for threshold voltage, body effect and gain associated with n and p-devices to be Independently optimized.

comparisions between cmos and Bipolar technologies

## cmos technology

- \* Low Static Power dissipation

- \* High Input Impedance (Low drive current)

- \* High Noise margin

- \* High Packaging density

- \* Low transconductance (2m)

- \* output current produced is Low

- \* Bidirectional capability

# Bipolar technology

- \* High Static Power dissipation

- \* Low Input Impedance

(High drive current)

- \* Low Noise margin

- \* Low Packaging density

- \* High transconductance

- \* output current produced is high

- \* unidirectional capability

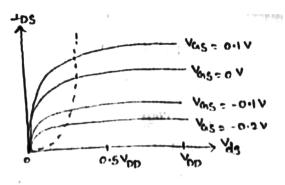

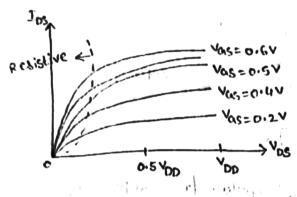

Drain-to-source current (Ids) versus drain-to-source voltage (ds)

relation ships :-

mos transistors are voltage controlled device. A voltage on the gate terminal Induces a charge in the channel that exists between source and drain. The charge then move from source to drain under the Influence of electric field generated by voltage Vis applied between drain and source.

The charge Induced is dependent on the gate to source Voltage Vas current IDs is dependent on both Vas and Vos.

The drain-to source current Ids is given by

$$I_{dS} = \frac{\text{charge Induced in } \cdot \text{channel } (\text{Qu}_{c})}{\text{Electron transit time } (\text{P})} = \frac{\text{Qu}_{c}}{\text{P}} - 0$$

Electron transit time,

$$1 \text{sd} = \frac{\text{Length of channel}}{\text{Velocity}} = \frac{1}{\sqrt{2}} - 2$$

where, u = mobility of holes (or) electrons Eds = Electric field (drain to source)

substitute en (1) in (3)

substitute en (5) in (2)

s. The electron and hole mobilities at room temperature um = 650 cm / v-sec , up = 240 cm / v-sec

Non-saturated region:-

The Average length along the channel is considered as  $\frac{V_{ds}}{2}$

\* Effective gate voltage Vg = Vgs-Vt

where  $V_t$  = threshold voltage is needed to Invert the charge under the gate and to establish the channel.

The charge per unit area = Eg &o Eins — (5)

where, Eo > permittivity of free space (8.854 x 1014 Flcm)

Eins -> Relative Permitivity of Insulation between gate and channel (5102=47

Eg - Average electric field gate to channel

consider

$$E_g = \left( \frac{V_{OS} - V_L}{D} - \frac{V_{dS}}{2} \right)$$

where D -> oxide thickness

substitute er 1 in er 1

$$I_{dS} = \frac{\varepsilon_0 \underbrace{\varepsilon_{ims} \omega \kappa}_{D} \underbrace{\left( (v_{dS} - v_{e}) - \frac{v_{dS}}{\lambda} \right)}_{A \ V_{dS}}}{\underbrace{\left( (v_{dS} - v_{e}) - \frac{v_{dS}}{\lambda} \right)}_{E}}_{C} = \underbrace{\varepsilon_0 \underbrace{\varepsilon_{ims} \omega A^*}_{LD} \left( (v_{dS} - v_{e}) - \frac{v_{dS}}{\lambda} \right) v_{dS}}_{C}$$

=

$$\frac{\varepsilon_0 \varepsilon_{ims} H}{D} \cdot \frac{\omega}{L} \left[ (495 - V_E) - \frac{V_{dS}}{2} \right] V_{dS} - 9$$

$$= \frac{\kappa \omega}{L} \left[ \left( \sqrt{g_S - v_E} \right) - \frac{\sqrt{d_S}}{2} \right] \sqrt{d_S} - \left( \frac{1}{2} \cdot \kappa - \frac{\varepsilon_0 \varepsilon_{ims} u}{D} \right)$$

$$I_{ds} = \beta \left[ (Y_{gs} - Y_{t}) - \frac{Y_{ds}}{2} \right] Y_{ds} - \left[ \vdots \beta = \frac{K \omega}{L} \right]$$

substitute ev 1 in 1,

$$I_{ds} = \frac{c_g A_I}{L^2} \left[ \left( \frac{V_{gs} - V_E}{2} \right) - \frac{V_{ds}}{2} \right] V_{ds}$$

(3)

consider

$$c_g = c_0 \omega L$$

— (4)

substitute ev@ in ev 3

$$T_{dS} = \frac{c_0 \omega 4}{L} \left( (v_{gS} - v_E) - \frac{v_{dS}}{2} \right) v_{dS} \qquad (S)$$

In this region, consider Yas = Ys-vt.

early becomes

$$I_{dS} = \frac{k_{UV}}{L} \left[ (V_{9S} - V_{E}) - (V_{9S} - V_{E}) \right] (V_{9S} - V_{E}) \qquad \left[ :: V_{dS} = V_{9S} - V_{E} \right]$$

$$= \beta \left[ (V_{9S} - V_{E})^{2} - (V_{9S} - V_{E})^{2} \right] \qquad \left[ :: \beta = k_{U} \right]$$

$$= \beta \left[ \left( (V_{9S} - V_{E})^{2} - (V_{9S} - V_{E})^{2} \right) - (\tilde{D}) \right]$$

Now, Jate per channel capacitance  $c_g = e_0 \frac{e_{instul}}{D}$

eq @, becomes

consider cg = cocol

$$= \int_{as}^{as} \frac{c_0 \omega \kappa u}{a \kappa} \left[ \left( \frac{c_0 s - v_k}{s} \right)^2 \right]$$

$$= \int_{as}^{as} \frac{c_0 \omega u}{a \kappa} \left[ \left( \frac{c_0 s - v_k}{s} \right)^2 \right] - \left( \frac{c_0 \omega u}{s} \right)^2$$

The current in 3 regions

-1.

Spital State State

a) pepletion mode device

b) Enhancement mode device

mos transistor threshold voltage (Nt)

For switching an enhancement mode most transistor from OFF to ON state, applying sufficient gate voltage to neutralize these charges and enable the underlying silicon to undergo an inversion due to electric field from the gate.

For switching an depletion made mos transistor from on to OFF state consists in applying enough voltage to the gate to add to state consists in applying enough voltage to the gate to add to the stored charge and Invert the 'n' Implant region to p-region.

The Threshold voltage (Vt) is given by

at - charge per unit area in the depletion layer

ouss - charge density at Si: Sioa Interface

& -> capacitance per unit gate area

Pms - work function différence between gate and silicon

of > Fermisevel Potential between inverted surface and bulk silicon

To evaluate by, each devm is determined as follows

$$\phi_{PN} = \frac{kT}{2} \ln \left( \frac{n}{n!} \right) \text{ volts } -3$$

Ques = (1.5 to 8) x 108 coulomb/m depending on crystal orientation

where,

VSB -> substrate bias voltage (-ve wir to wmos, trefor pmos)

9 -> 1.6x1019 coulomb

N > Impurity concentration in substrate (NA (Or) ND)

Esi → Relative permitivity of silicon (≈11.7)

n; > Intrinsic electron concentration (16 x 16 cm3 at 300 k)

k → Boltzmann's constant (+4×1023 Joule ok)

Alternative expression for Vt in terms of VsB is as follows

where  $V_{\xi}(0) \rightarrow$  Threshold voltage for  $V_{SB}=0$

D -> oxide thickness

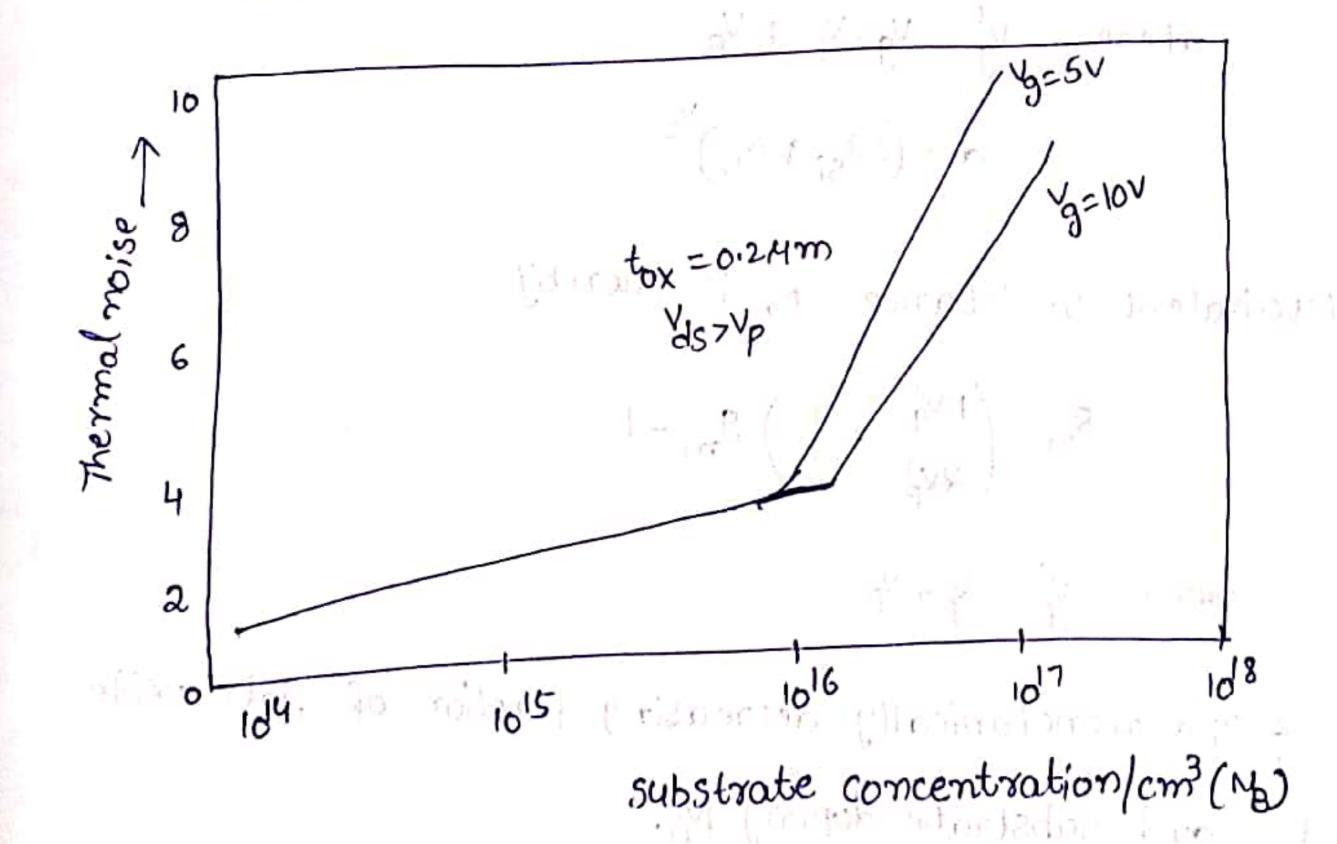

Body effect :-

Increasing YsB causes

the channel to be depleted

of charge carriers and thus

the threshold voltage is raised.

The variation of threshold voltage due to source to substrate voltage is referred as "Body effect".

The relation ship between threshold voltage and substrate bias voltage is given by

where 7 is constant it depends on substrate doping, so that more lightly doped the substrate, smaller will be body effect.

mos transistor transconductance (Im) and output conductance (Is) :-

Transconductance (9m):-

It is defined as the ratio of soutput current to the change in

Input voltage by taking output voltage is constant

$$g_{m} = \frac{s I_{ds}}{s v_{gs}}$$

$v_{ds} = constant$

we know that

$$I_{dS} = \frac{\alpha_{\ell}}{\gamma_{\ell d}} \Rightarrow SI_{dS} = \frac{S\alpha_{\ell}}{\gamma_{\ell d}} - 2$$

But

$$\frac{1}{5d} = \frac{1^{2}}{44 \text{ Vds}}$$

—3

substitute ev@ in ev@

we know that, shange in charge a=cv

substitute evo in eva

under saturation region, Vds = 48-Vb

$$9_m = \frac{c_g \mathcal{H} \left( \frac{v_{gS} - v_E}{L^{\nu}} \right)}{L^{\nu}} - 8$$

we know that

$$c_g = \frac{\epsilon_0}{D} \frac{\epsilon_{inscul}}{D}$$

substitute ev 1 in ev 1

$$= \underbrace{k \cdot \omega}_{L} \left[ v_{gs} - v_{t} \right]_{0}^{+} \left[ v_{ss} - v_{t} \right]_{0}^{+}$$

$$\vartheta_{s} = \frac{s \tau_{ds}}{s v_{ds}}$$

$$= \lambda \cdot \tau_{ds} = \left(\frac{1}{L}\right)^{\nu}$$

From above equation, 2dt and Isat

mos transistor figure of merit (ab) 1-

The figure of merit is a quantity used to characterized the performance of a device related to other devices of same time.

It is defined as the ratio of transconductance to the gate-tochannel capacitance

$$\omega_{0} = \frac{g_{m}}{cg} = \frac{\sqrt{g}}{L^{\nu}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

$$= \frac{\sqrt{g}}{\sqrt{g}} \qquad \left[ :: g_{m} = \frac{c_{g}}{4} \frac{\sqrt{g} s^{-\nu} \epsilon}{L^{\nu}} \right]$$

From ev O, switching speed depends on i) carrier mobility

- ii) Inversly on sociare of channel len

- randon de la parti de la gardii) gate voltage

A high speed switching circuits, high Im as possible.

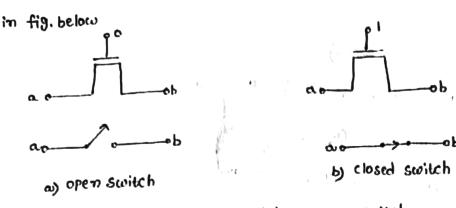

The transistor can be used as an on-off switch as shown

Fig: mos bransistor as a switch

\* The switch is turned off by setting ys=0, the channel disappears and a small amount of leakage current flows at the drain end.

\* consider ys = YDD, the switch is turned on, the current flows through it.

If the gate and drain are pass transistor are both HIGH, the source will rise to the lower of two Potentials.

S= Le Vod-Yth \* If the gate and drain are both at VDD the source can only rise

to one threshold voltage below through gate.

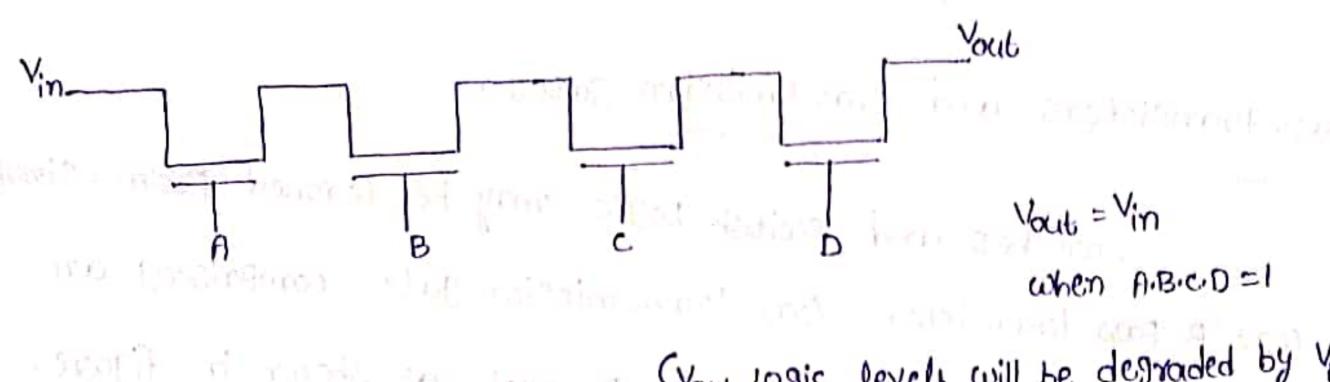

A number of transistors can be used as switches in series (E) in switching logic arrays. An AND array as shown in fig.

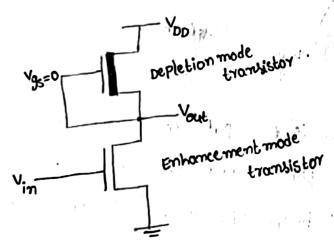

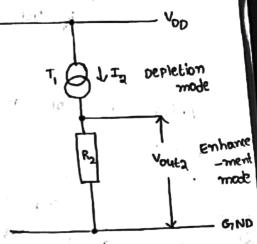

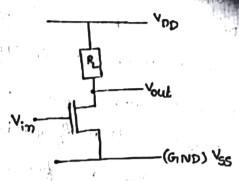

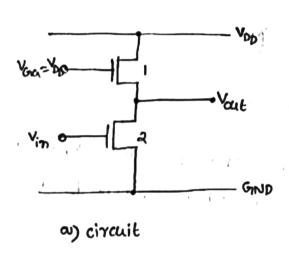

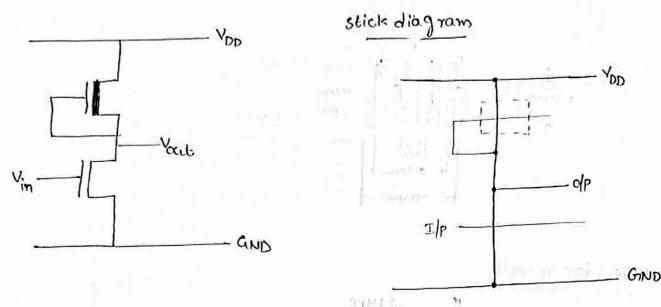

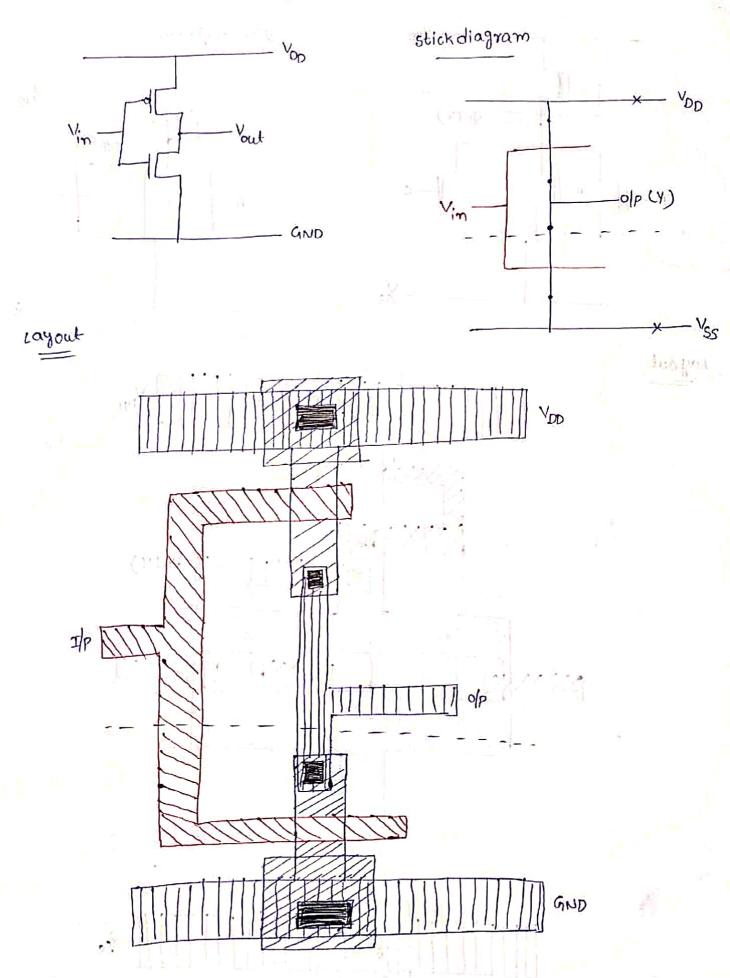

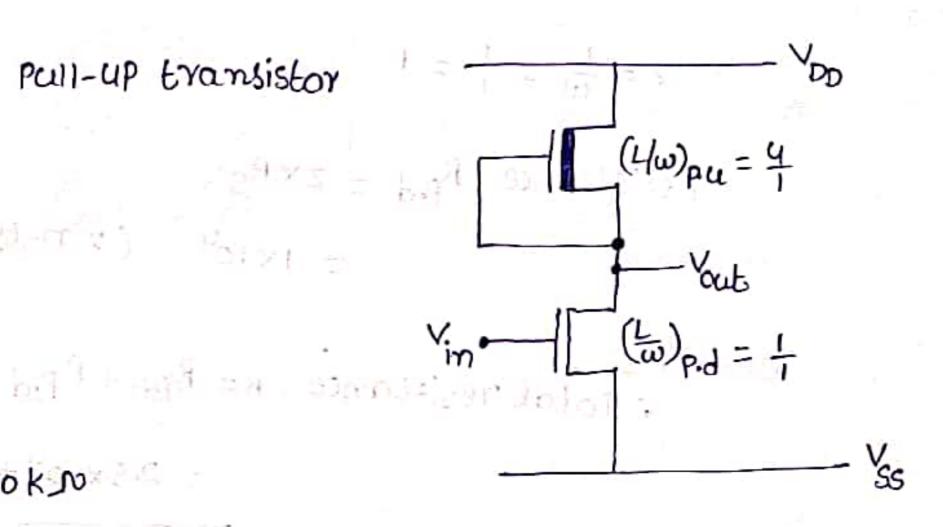

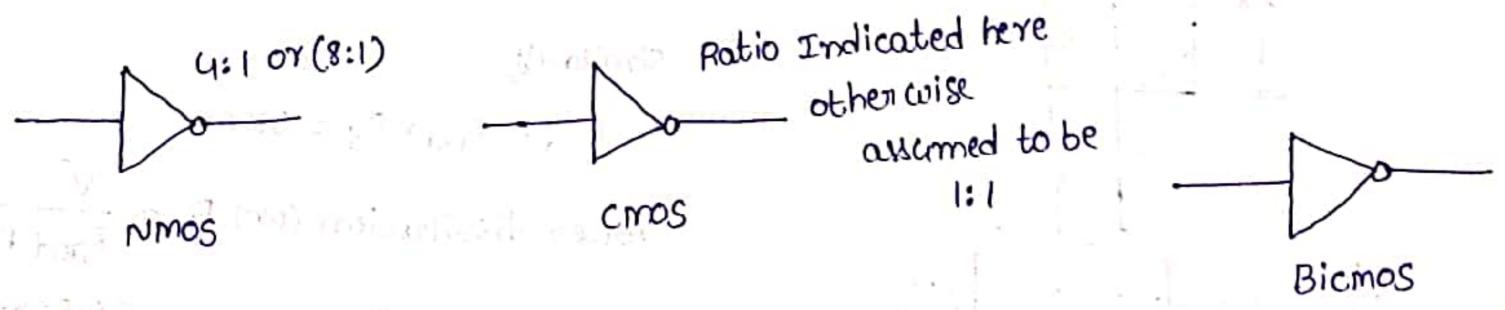

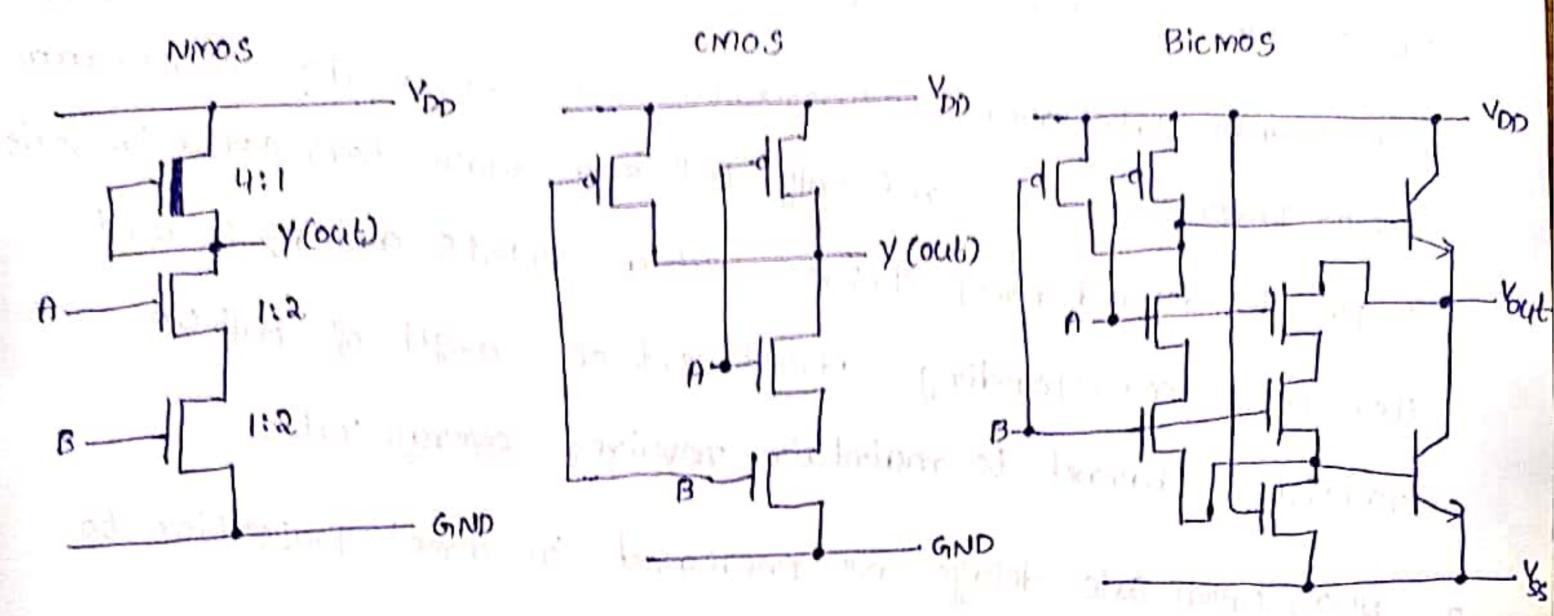

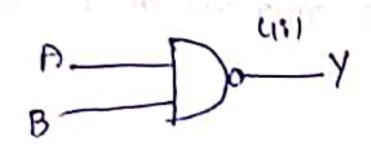

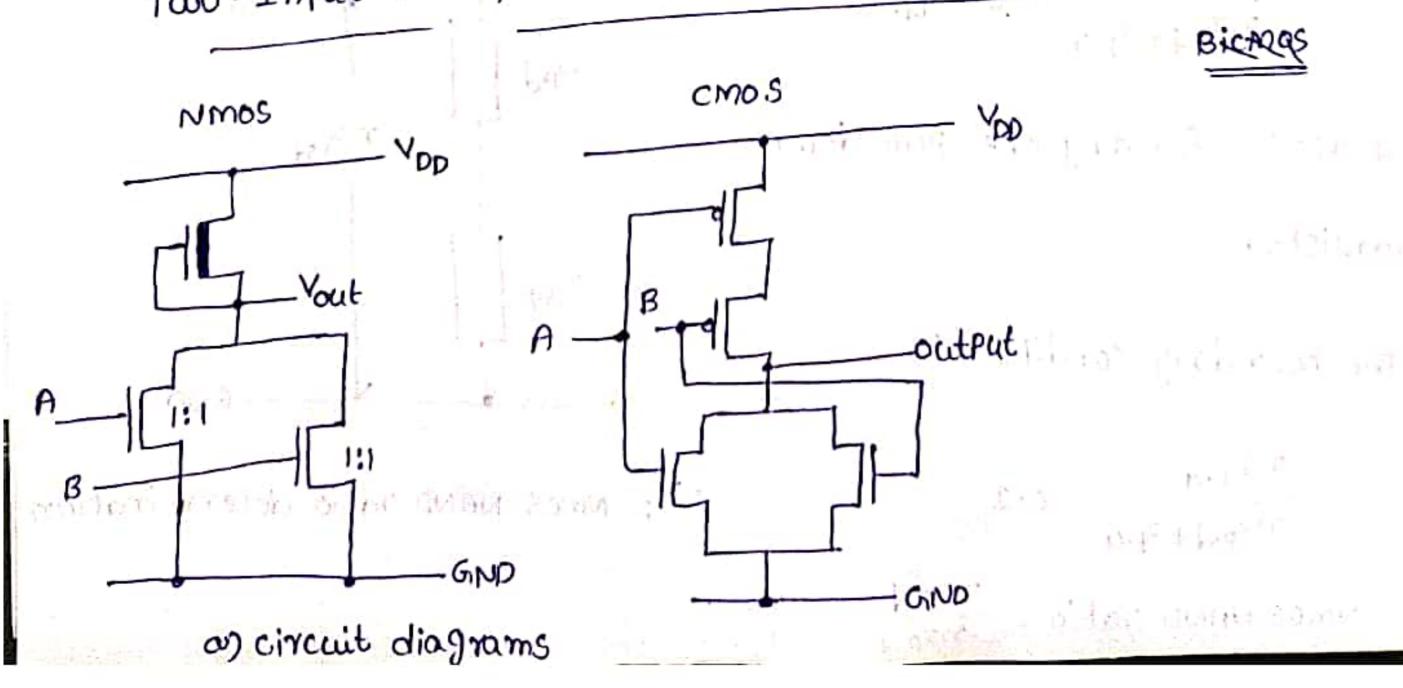

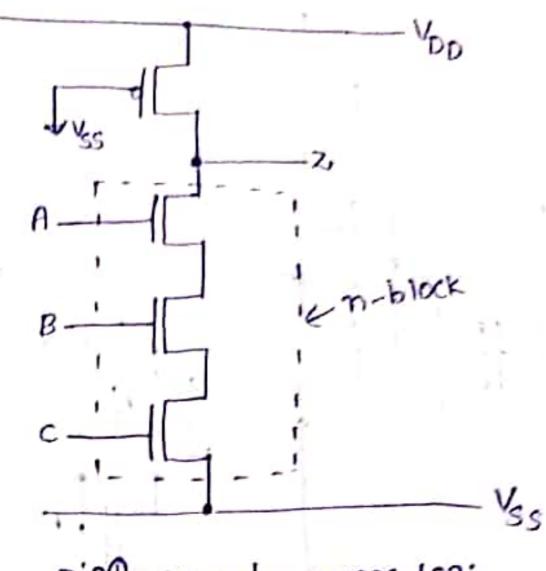

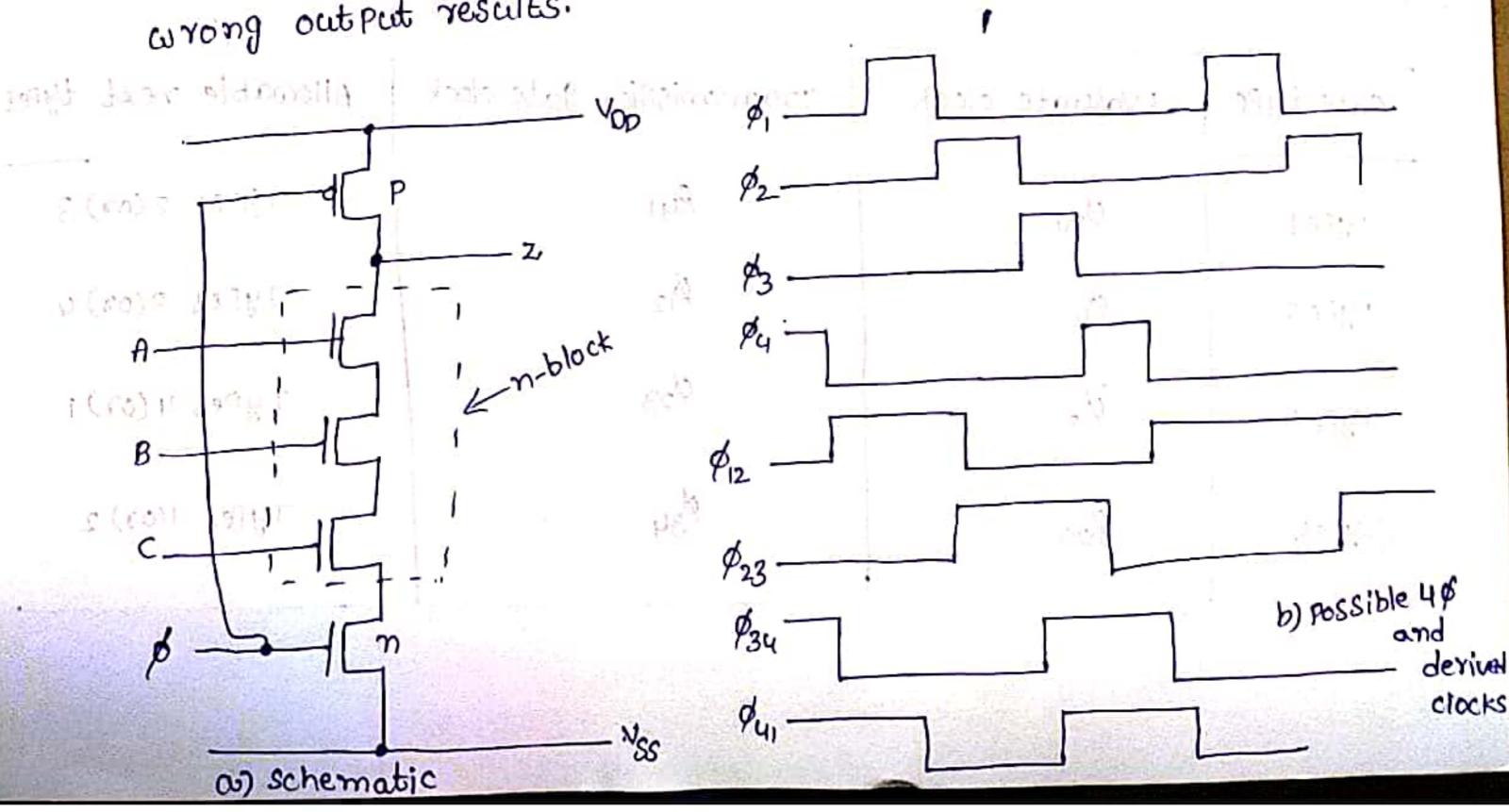

### Nmos Inverter:

The basic Inverter circuit requires a transistor with source connected to ground and a load resistor of some sort connected from the drain to positive supply rail Yop. The output is taken from the drain and the Input applied between gate and ground.

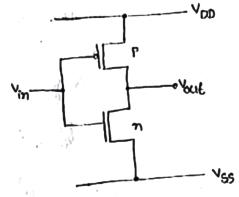

The NMOS Inverter circuit as shown in fig.

In this configuration, with no current drawn from the output, the current IDS for both transistors are equal.

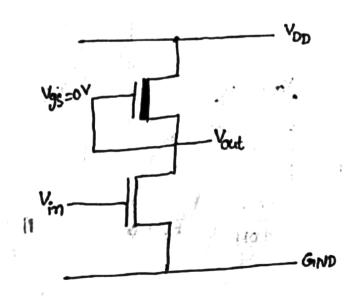

For the depletion mode transistor, gate is connected to the Source so it is always on and only the characteristic curve Vis=0 is relevant.

In this configuration the depletion made device is called the pull-up (AU) and enhancement made device is called the pull-down (AD) transistor.

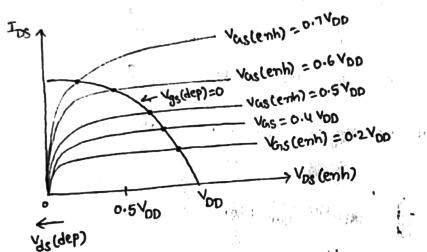

by superimposing Vasto depletion mode characteristic curve on the family of curves for the tenhancement mode device with the condition the maximum voltage across the enhancement mode device corresponds to minimum voltage across the depletion mode device.

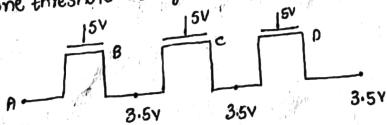

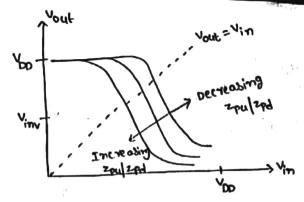

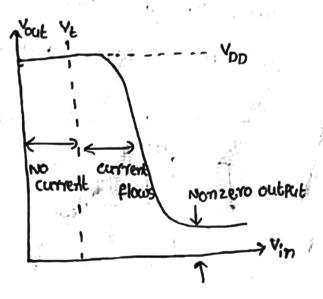

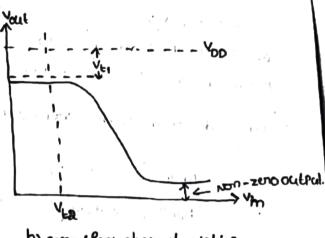

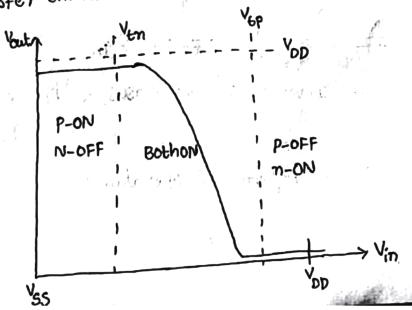

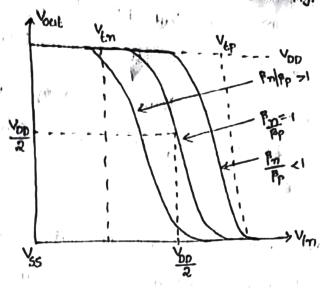

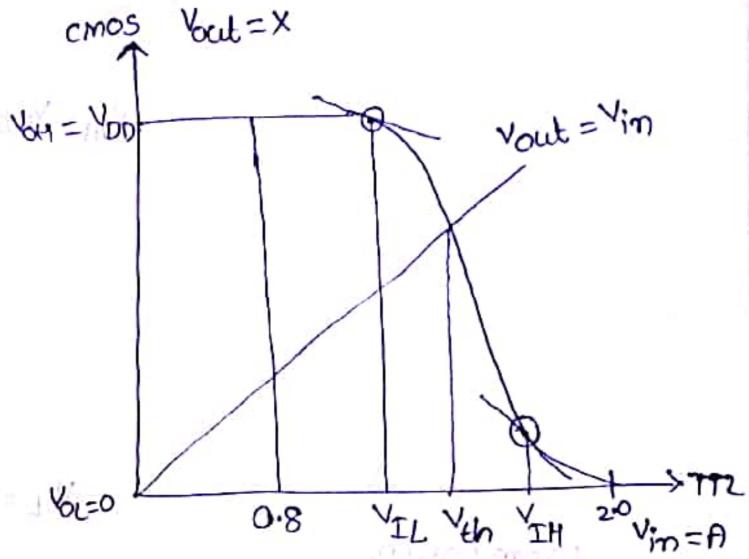

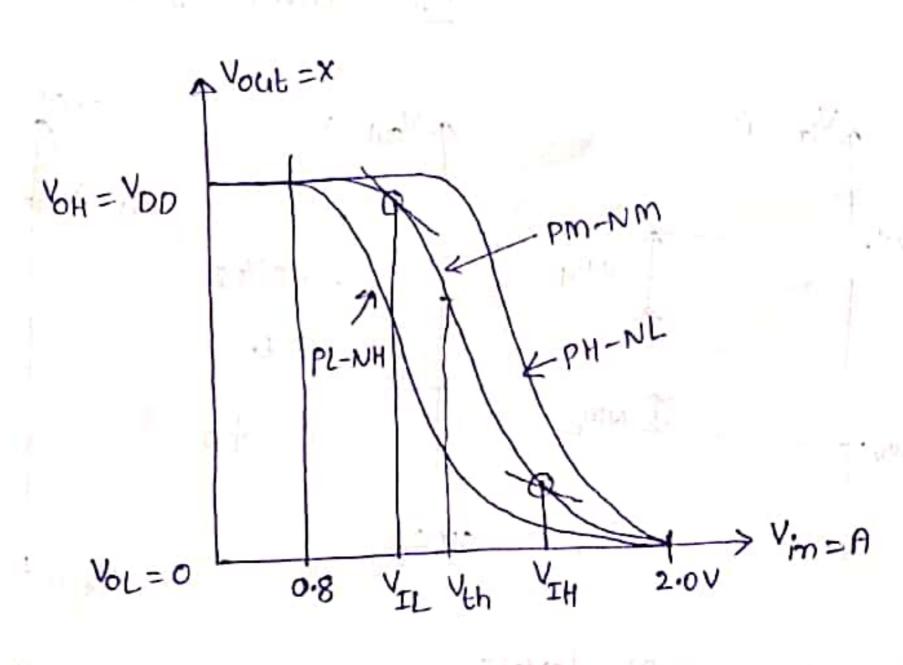

The transfer characteristics of NMOS Inverten as shown in fig.

Now the Input Voltage Vin is the gabe-to-source voltage Vas for the pull down transistor. As this exceeds the threshold voltage of pull down transistor, current begins to flow. This causes the output pull down transistor, current begins to flow. This causes pull down voltage Vout to decrease and further Increase in Vin causes pull down transistor to some out of saturation and become resistive.

• Definition of the section of the s

Scanned with CamScanner

Scanned with CamScann

11,

Fig: Nmos Inverter transfer characteristics

The point on the transfer characteristic at which Vout = Vin is denoted as

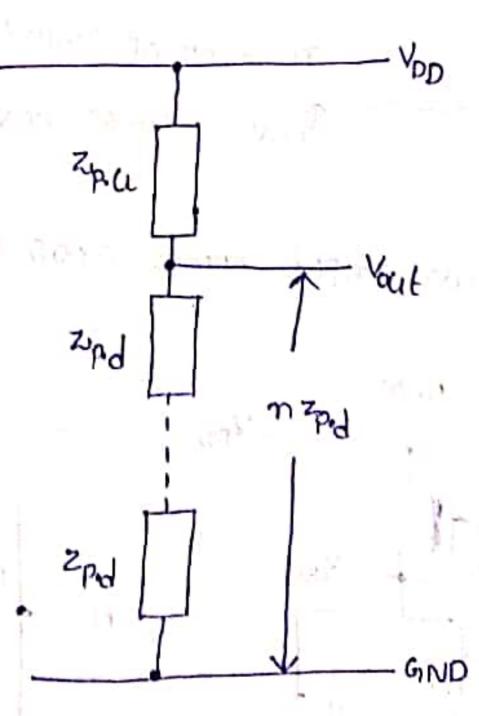

Determination of pull-up to pull-down ratio (zpu|zpd) for an Nmos Inverter :-

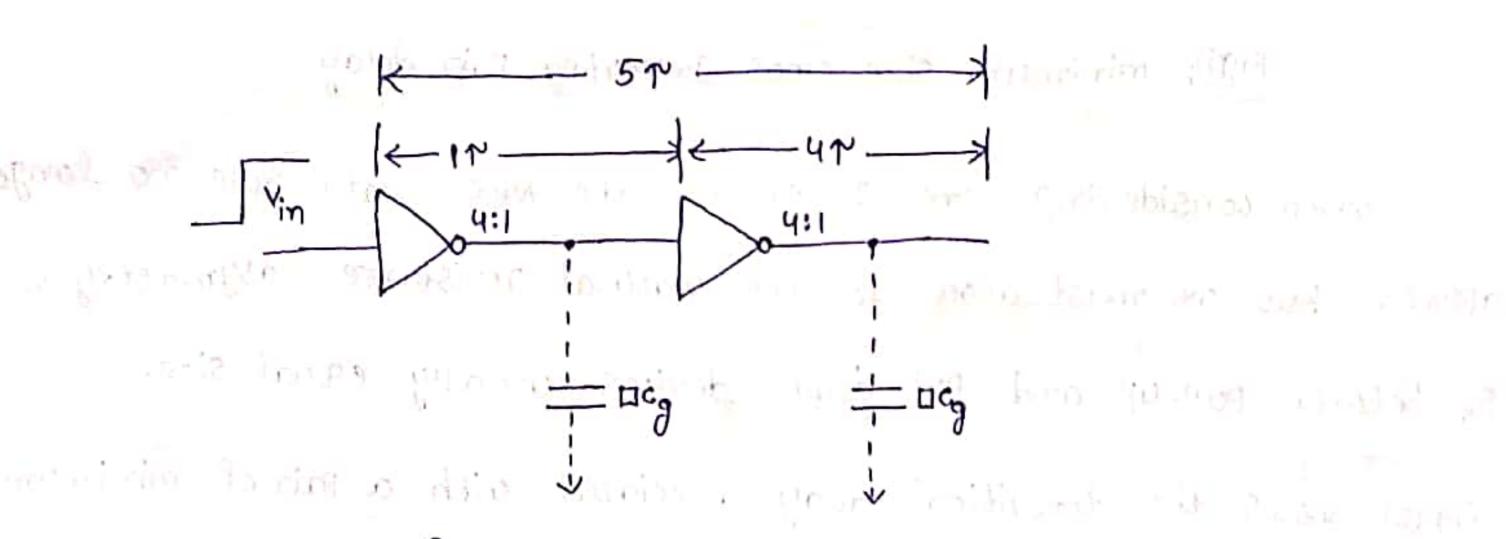

consider two Inverters are arranged in a cascaded manner.

These two are operate in a Saturation region.

The depletion mode transistor for which Vgs=0, so maximum drain current flows i.e all devices are on.

For equal margins around the Inverter threshold, we said  $V_{inv} = 0.5 \, V_{DD}$  at this Point both the transistors are in Saturation.

we know that,

Ids =

$$\frac{k\omega}{L} \left[ \left( \frac{(v_{gs} - v_{e})^{2}}{2} \right] - 0 \right]$$

[: saturation region

In depletion mode

$$T_{dS} = K \cdot \frac{\omega_{pu}}{L_{pu}} \left[ \frac{(y_{S} - V_{k})^{2}}{2} \right]$$

$$= K \cdot \frac{\omega_{pu}}{L_{pu}} \left[ \frac{(-V_{kd})^{2}}{2} \right] - 2 \quad [: V_{gs} = oV]$$

For enhancement mode,

$$I_{ds} = k \cdot \frac{\omega_{pd}}{L_{Rd}} \left[ \frac{\left( V_{inv} - V_{E} \right)^{2}}{2} \right] - 3 \quad \left[ :: V_{gs} = V_{inv} \right]$$

equating ev 1 & 3)

$$\left[ \frac{\omega_{\text{Pu}}}{L_{\text{Pu}}} \left[ \left( -\frac{V_{\text{td}}}{2} \right)^{2} \right] = K \frac{\omega_{\text{Pd}}}{L_{\text{Pd}}} \left[ \frac{\left( V_{\text{imV}} - V_{\text{E}} \right)^{2}}{2} \right]$$

The Aspect ratio (2) is defined as the ratio of length to the width.

$$\frac{1}{z_{pq}} \left[ \left( \frac{-v_{td}}{z} \right)^{\gamma} \right] = \frac{1}{z_{pd}} \left[ \left( \frac{v_{inv} - v_{t}}{z} \right)^{\gamma} \right]$$

$$\Rightarrow (v_{inv} - v_{b})^{2} = \frac{2pd}{2pu} \left[-v_{bd}\right]^{2}$$

$$V_{inv} - V_t = \frac{-V_{td}}{\sqrt{\frac{z_{pu}}{z_{pd}}}} - \Psi$$

substitute typical values of

$$0.5 V_{DD} - 0.2 V_{DD} = \frac{0.6 V_{DD}}{\sqrt{\frac{2pu}{2pd}}}$$

$$\sqrt{\frac{2pu}{2pd}} = \frac{0.6 V_{DD}}{0.3 V_{DD}}$$

$$\frac{2pu}{2pd} = (\frac{2}{1})^{2} = \frac{1}{1} = \sqrt{\frac{2pu}{2pd}} = \frac{1}{1}$$

$$= 4:1$$

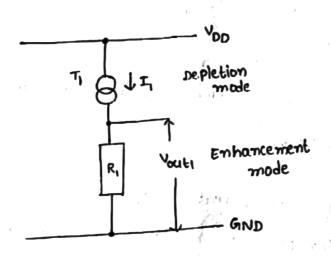

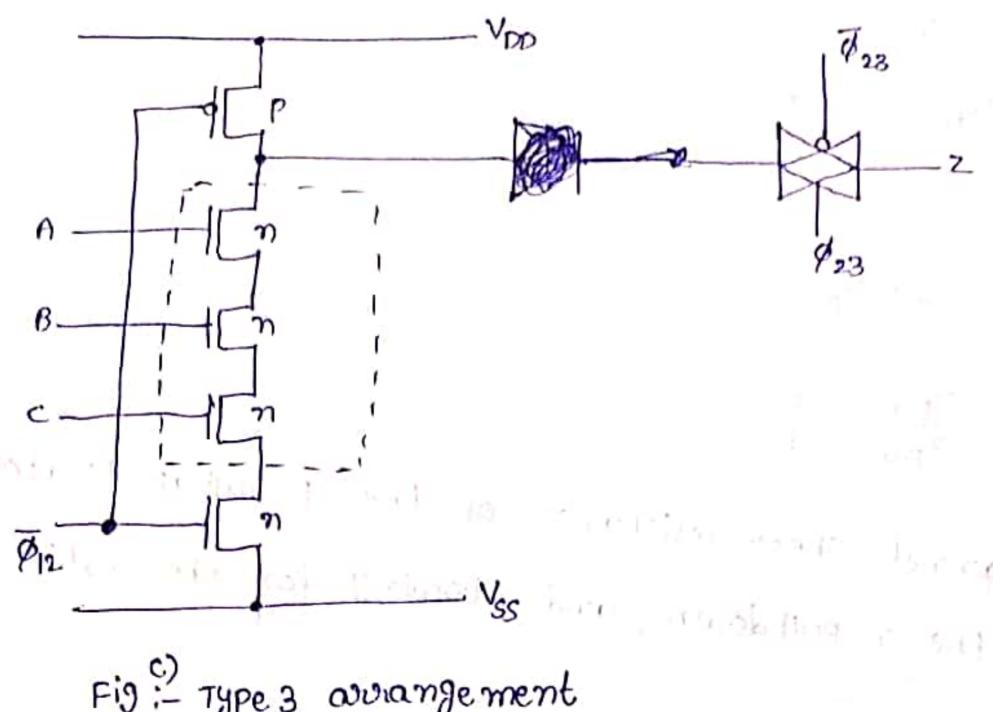

Determination of Zpu/zpd ratio for an ismos Inverter driven through one (or) more pass transistors:

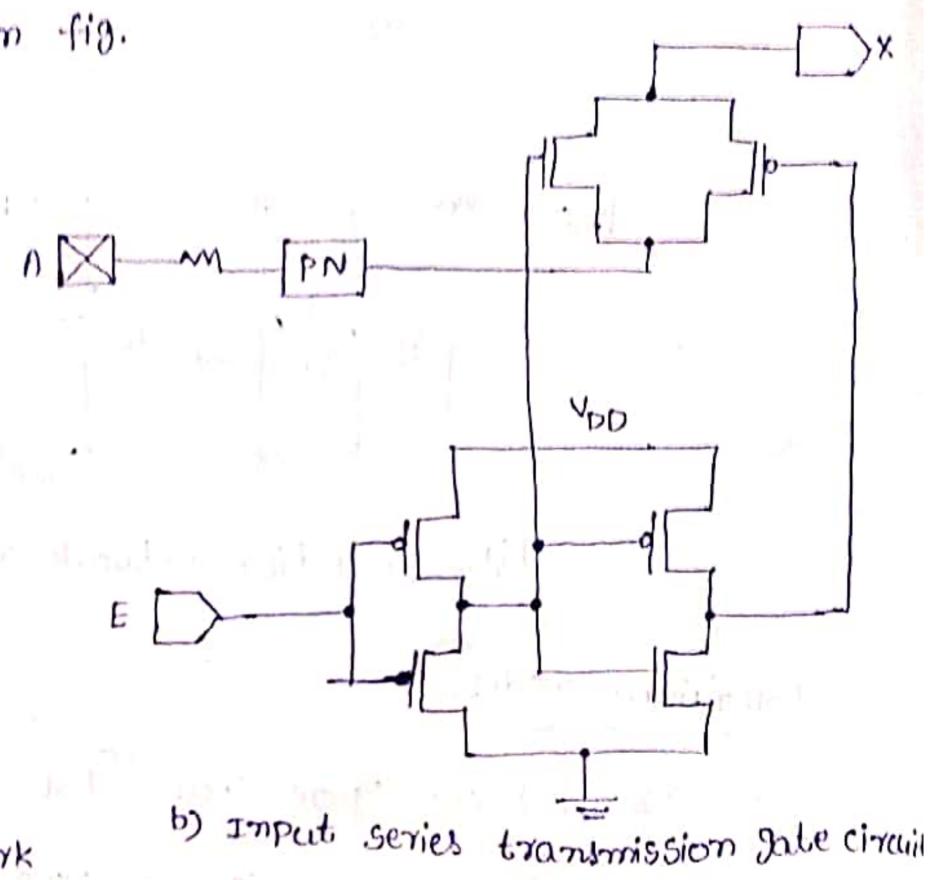

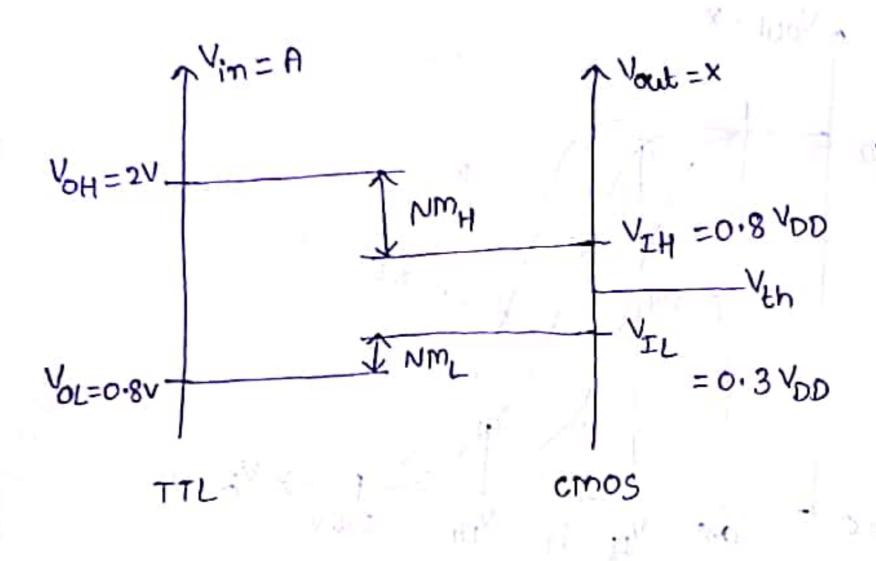

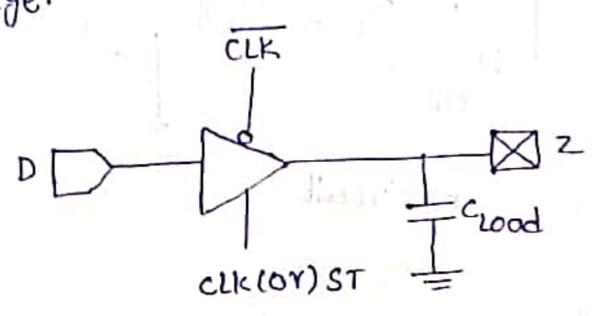

some times the Inpub to an Inverter may come from the output of an Inverter but after passing through one (or) more remos transistors that are used as pars transistors. The arrangement as shown in fig.

when A in is at ovolts, Bis at Vop, but the voltage into Inverter 2 at point c has got reduced from 400 by threshold voltage of series pass transistor. There is a reduction in voltage by tp where Up is the threshold voltage.

Hence Imput voltage to Inverter 215

when Input to Inverter 1 is VDD, its pull down transistor conducting with a low voltage across it. At the same time,

the Pull-up transistor T, is in saturation and represented as a current source.

The equivalent dircuits of Inverters 1 & Inverter a as shown in fig.

a) Inverter 1 with Imput = VDD

b) Inverter 2 with Input = VDD - VEP

pull down transistor,

$$R_{1} = \frac{V_{DS1}}{T_{DS}}$$

$$= \frac{V_{DS1}}{V_{DS1}} \left[ \frac{V_{DD} - V_{E} - \frac{V_{dS}}{2}}{V_{DS1}} \right] V_{SS}$$

$$= \frac{1}{K} \cdot \frac{U_{Pd1}}{U_{Pd1}} \left[ \frac{V_{DD} - V_{E} - \frac{V_{dS}}{2}}{V_{DS1}} \right] V_{SS}$$

Ves is small and hence it can be neglected

$$R_1 = \frac{1}{K} PdI \frac{1}{(V_{DD} - V_t)} - 0$$

$$I_1 = I_{AS} = \frac{K}{L_{PQ1}} \left[ \frac{(V_{DS} - V_{Ed})^2}{2} \right]$$

consider Ys= 00

$$J_1 = k \cdot \frac{\omega_{\text{put}}}{L_{\text{put}}} \left[ \left( -\frac{V_{\text{bd}}}{2} \right)^{k} \right]$$

The output of Inverter 1, Voul = TRI

$$V_{out_1} = K \cdot \frac{\omega_{pu_1}}{L_{pu_1}} \left[ \left( \frac{-V_{td}}{2} \right)^{\nu} \right] \cdot \frac{1}{K} \cdot \frac{z_{pd_1}}{z_{pd_1}} \left( \frac{-V_{td}}{V_{DD} - V_{t}} \right)$$

$$= \frac{1}{z_{pu_1}} \left[ \left( \frac{-V_{td}}{2} \right)^{\nu} \right] \cdot \frac{z_{pd_1}}{z_{pd_1}} \left( \frac{-V_{td}}{V_{DD} - V_{t}} \right)$$

$$= \frac{2Pd1}{2Pu1} \cdot \frac{(-V_{td})^2}{2(V_{DD}-V_t)} = 2$$

consider Inverter & with Input as You-YEP

$$I_{a} = k \cdot \frac{1}{2pua} \left[ \left( -\frac{V_{td}}{2} \right)^{2} \right] - \Theta$$

The output of Inverter 2, Vout 2 = IzR2

Vout

$$a = K \cdot \frac{1}{2pua} \left[ \left( \frac{-V_{td}}{2} \right)^{2} \right] \cdot \frac{1}{kr} \frac{2pda}{pda} \left[ \left( \frac{V_{DD} - V_{tp}}{V_{DD} - V_{tp}} \right) - V_{t} \right]$$

$$= \frac{z_{Pd2}}{z_{pu2}} \cdot \frac{1}{(v_{DD}-v_{tp})-v_t} \cdot \frac{(-v_{td})^2}{2} - 5$$

The output of Inverter 2 is same as the inverter 1

$$V_{\text{out},1} = V_{\text{out},2},$$

$$T_1 R_1 = T_2 R_2.$$

$$\frac{\overline{z_{Pd1}}}{\overline{z_{Pd1}}} \cdot \frac{(-V_{td})^{2}}{\overline{z_{Pd2}}} = \frac{\overline{z_{Pd2}}}{\overline{z_{Pd2}}} \cdot \frac{1}{(V_{DD} - V_{tP}) - V_{t}} \cdot \frac{(-V_{td})^{2}}{\overline{z_{Pd2}}}$$

$$\frac{z_{\text{Pdl}}}{z_{\text{Pul}}} \cdot \frac{(-v_{\text{td}})^2}{\sqrt{2}} \cdot \frac{1}{v_{\text{DD}} - v_{\text{t}}} = \frac{z_{\text{Pda}}}{z_{\text{Pua}}} \cdot \frac{1}{(v_{\text{DD}} - v_{\text{tp}})^{-v_{\text{t}}}} \cdot \frac{(-v_{\text{td}})^2}{2}$$

substitute vt = 0.2 VDD, Vtp = 0.3 VDD in eq 6,

$$\frac{z_{PUR}}{z_{PdR}} = \frac{z_{PUR}}{z_{PdR}} \cdot \frac{v_{OD} - 0.2 v_{DD}}{(v_{DD} - 0.3 v_{DD}) - 0.2 v_{DD}}$$

$$= \frac{z_{PUR}}{z_{PdR}} \cdot \left[ \frac{0.8 v_{DD}}{0.5 v_{DD}} \right] \approx \frac{z_{PUR}}{z_{PdR}} \cdot \left[ \frac{0.8 v_{DD}}{z_{PdR}} \right]$$

$$= \frac{z_{PUR}}{z_{PdR}} \cdot \left[ \frac{8}{5} \right]$$

Therefore an Inverter driven through one (or) more pass transistors as a zpu/zpd is greater than 8/1.

Scanned with CamScanner

## Alternative forms of Pull-up :-

#### 1. Load resistance (Ri) :-

flows from Vob to Vss.

If logic 1' is given at Vin, there is a current flows from Vpo to Vss.

of the large space requirements of resistor.

Produced in Silicon substrate.

Fig:- Resistor Pull-up

#### 2. Nmos depletion mode transistor pull-up:

- e) Dissipation is high since rail to rail current flows when Vin= Logical 1

b) switching of output from 1 to 0 begins when Vin exceeds 4 of

pull down device.

- non-saturated initially, this Process presents lower resistance through which to charge capacitive loads.

a) circuit

b) Transfer characteristics

## 3. Nmos enhancement mode pull-up :-

- \* Dissipation is high since current flows when Vin = logical 1

- \* Your can never reach by (Logical 1) if You = You as is normally the case

- \* You may be derived from a switching source, for example, one phase of a clock, so that dissipation can be greatly reduced. If you is higher than You, an extra rail is required

b) transfer characteristics

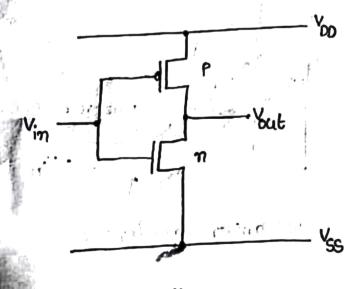

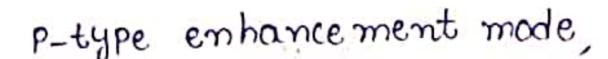

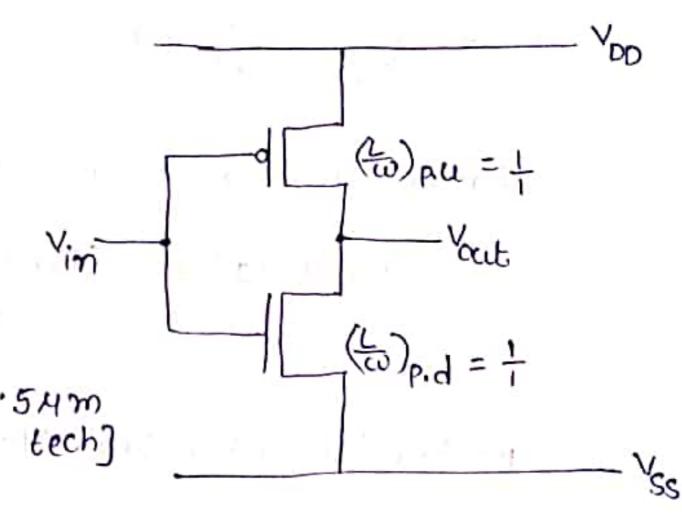

- 4. complementary transistor pull-up:

- -> No output current flow either for logical 1 (or) logical 0 Inputs.

- -> For similar dimension devices, the n-channel device is

faster than p-channel device.

an circuit

b) Transfer characteristics

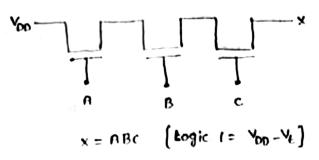

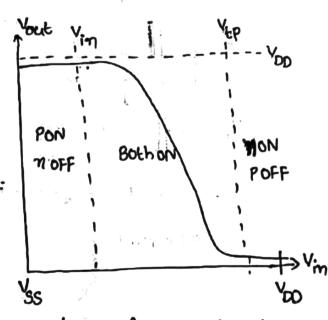

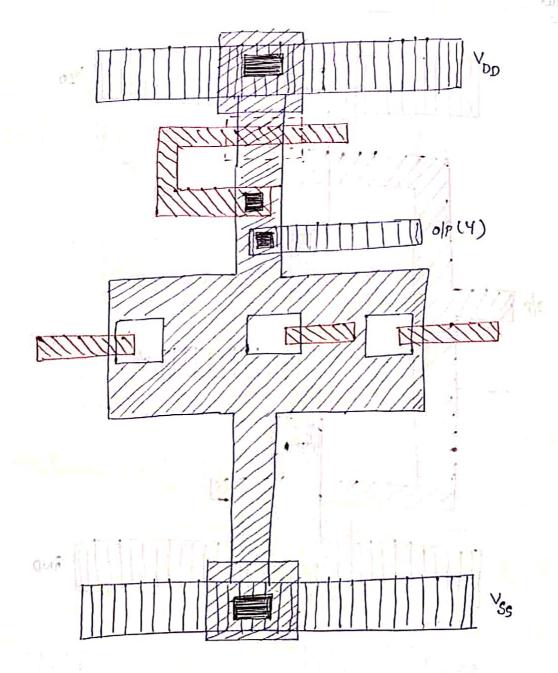

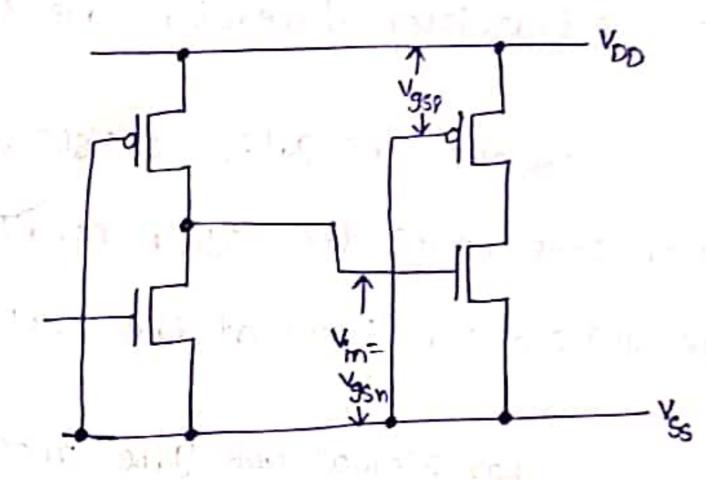

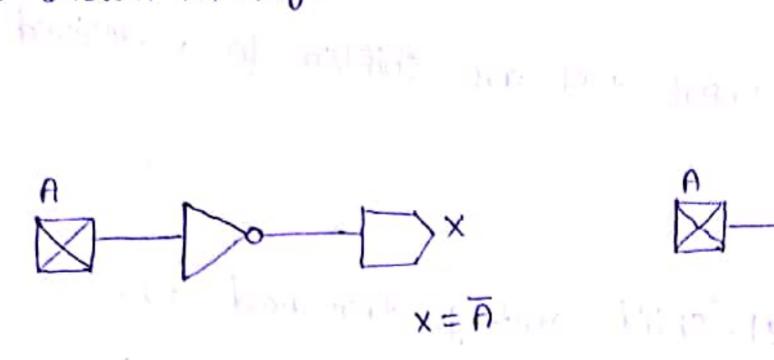

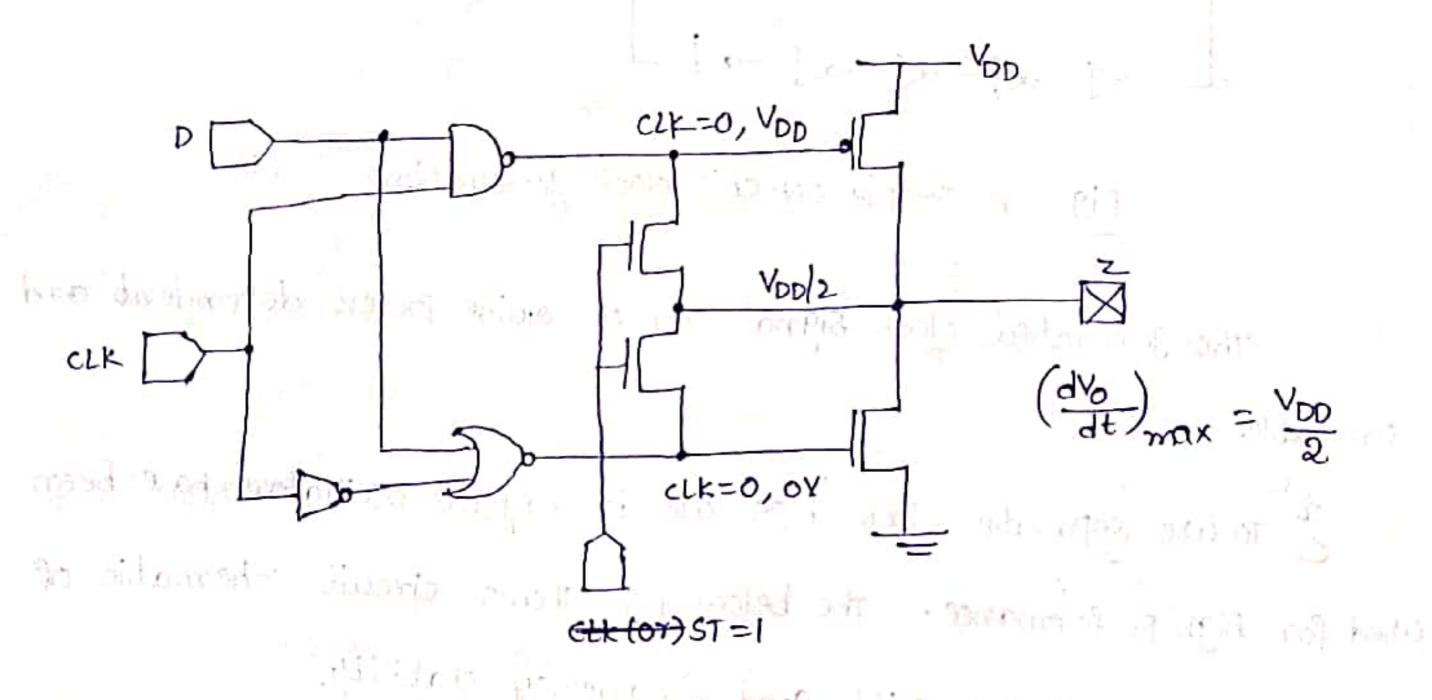

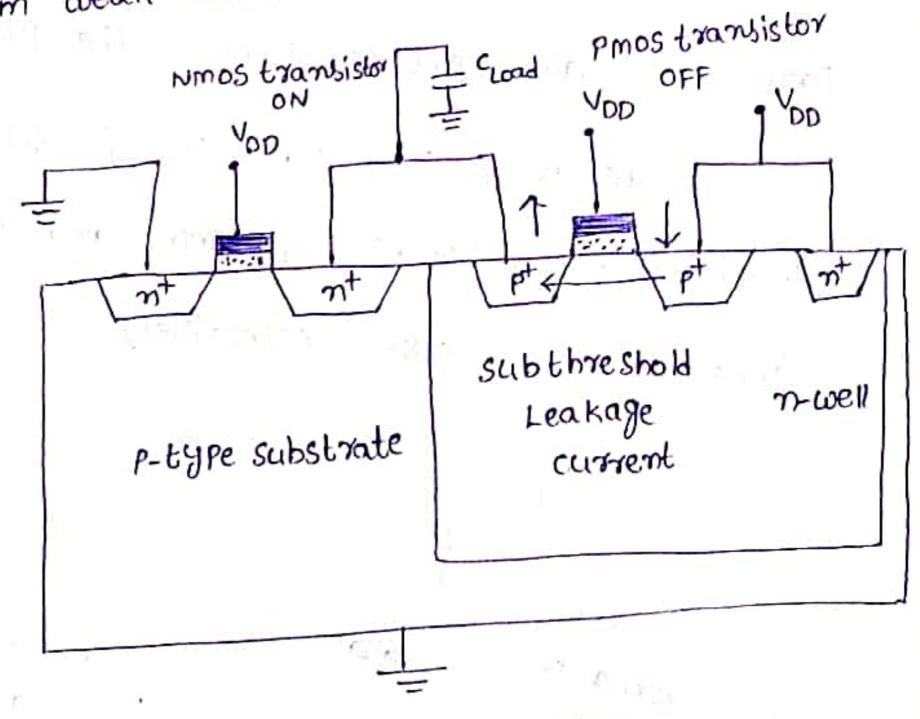

The cmos Inverter can be designed by using pmos and Nmos transistors.

The operation of the circuit as follows:

the Jate of the P-channel transistor is at You below the source Potential, i.e

Vos=Voo. This turns on this transistor, capacitor charged upto Voo.

Fig: cmos Inverter

transistor since Vas=0.

If the Input voltage incised to threshold voltage level of the n-channel transistor and then to VoD, n-channel transistor will conduct and p-channel transistor gets turned off, discharging the load capacitance to ground potential.

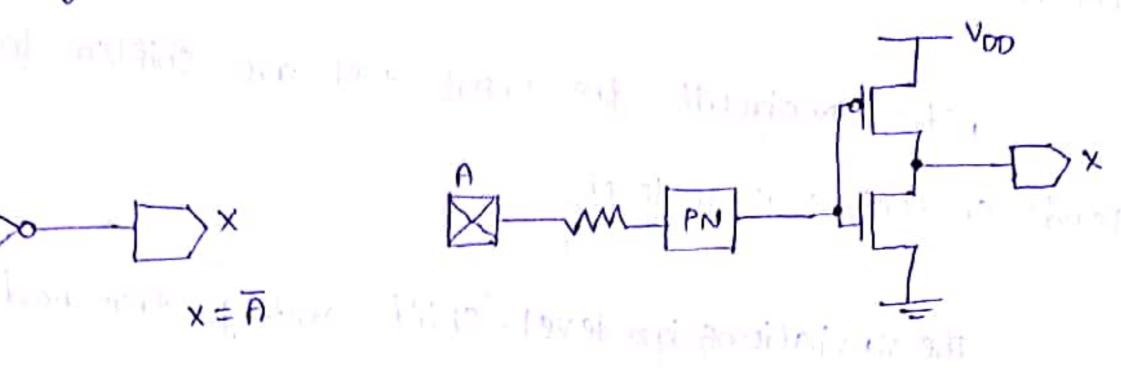

The transfer characteristics as shown in fig. below

The current / voltage relation ships for the mos transistor

$$I_{ds} = \frac{P}{3} \left( Y_{ds} - Y_{b} \right)^{\gamma} - 2 \left[ P = \frac{1}{2} \frac{\omega}{L} \right]$$

'B' applicable to both nmos and pmos transistors,

$$\beta_n = \frac{\epsilon_0 \epsilon_{ins} \alpha_n}{D} \frac{\omega_n}{L_n} - Q$$

Where up, wn, Lp, in one pand n-transistor dimensions.

Mp, un one hole and electron mobilities.

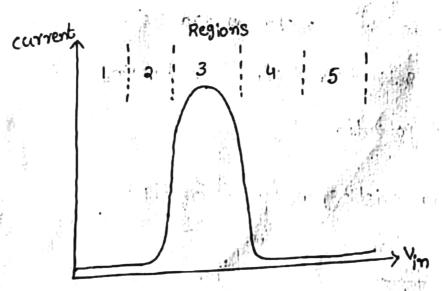

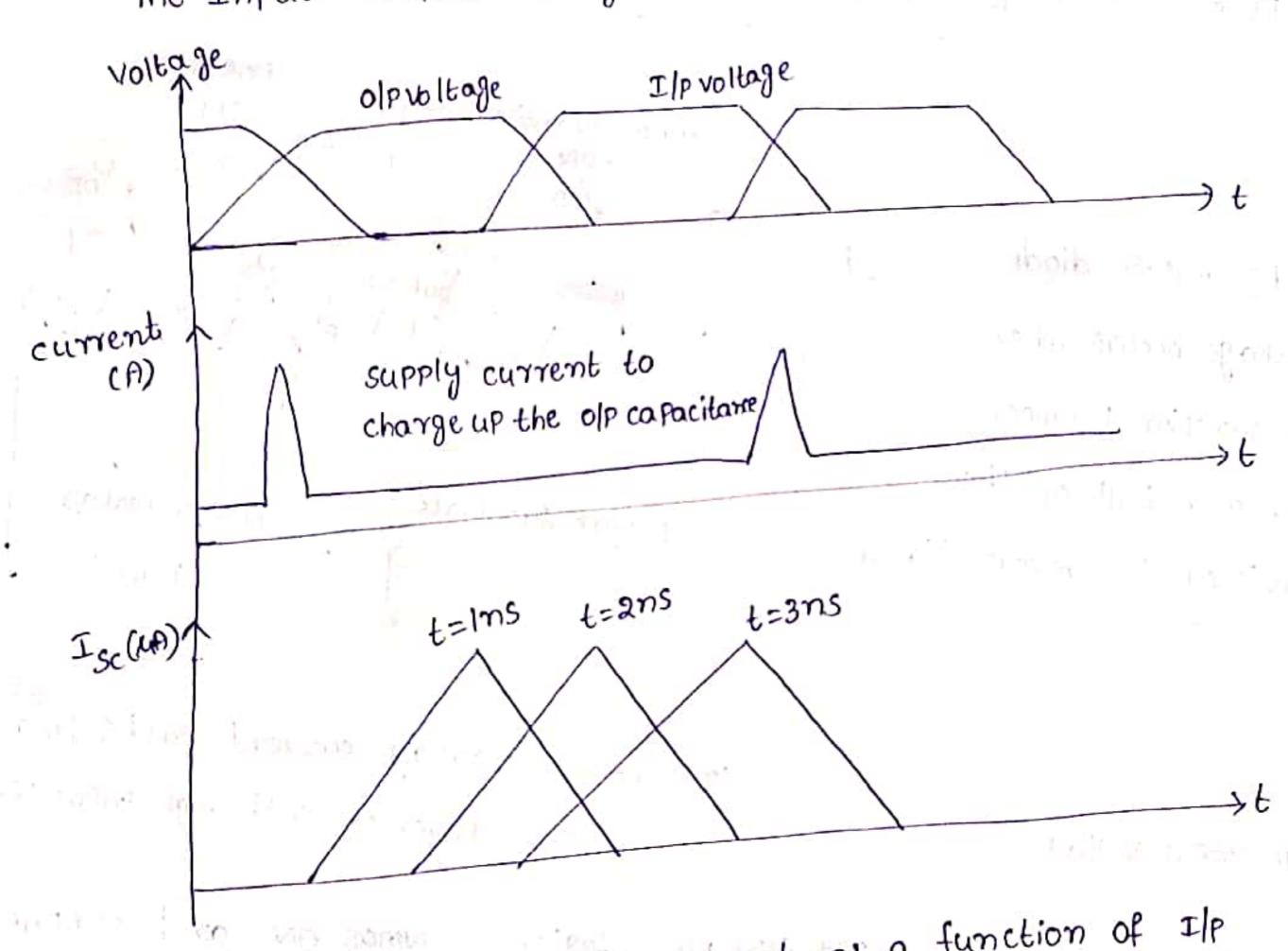

Fig: - cmos Inverter current versus Vin

It has five distinct regions of operations.

Vin = Logico = ov

PMOS is ON and NMOS is OFF. Hence no current flows through the Inverter circuit and output directly connected to YDD.

N-transistor on and P-transistor OFF. In this condition again no current flows through the circuit.

Vin > 1/6 (The Input Voltage is Increased above the Region 2:threshold voltage)

N-transistor conducts and has a very large difference between drain and source and is in saturation.

P-transistor also conducts, with only small voltage difference between drain and source it operates in unsaturated resistive region.

#### Region 4:

conditions are same as in region 2 but with the roles of P-and n-transistors reversed. That is, P-transistor has a large voltage across it while the n-transistor has a small voltage acrossit. The drain current in both the regions a and 4 is Small.

Large current flows in region 3. In this region, both the devices are in saturation.

since, the two transistors are in series, the current through them is same, we can write

$$\frac{1}{ds} = \frac{k\omega}{L} \left[ \frac{v_{9s} - v_{E}}{2} \right]^{\gamma}$$

(saturation)

$$\frac{1}{ds} = k \frac{\omega}{L} \left[ (4s - v_E)^2 ds - \frac{v_{1s}^2}{2} \right] \left[ \text{resistive} \right]$$

$$\omega kT$$

$I_{dS} = \frac{k\omega}{kL} \left[ v_{gS} - v_{E} \right]^{2}$

$$Idsp = \frac{K \omega_p}{4p} \left( \frac{V_{9S} - V_E}{2} \right)^2$$

$$= k \frac{\omega_P}{L_P} \left( \frac{V_{in} - V_{DD} - V_{LP}}{2} \right)^{2} \qquad \left[ : V_{gs} = V_{in} - V_{DD} \right]$$

$$V_{t} = V_{tP}$$

$$I_{dsn} = k \frac{\omega_n}{L_n} \left( \frac{v_{in} - v_{tn}}{a} \right)^{\gamma}$$

$$I_{dsn} = \frac{\beta_n}{2} \left( v_{in} - v_{kn} \right)^n - Q$$

Equating 0 & 2 we get

$$V_{in} = \frac{V_{DD} + V_{tp} + V_{tn} \left( \frac{\beta_n}{\beta_p} \right)^{1/2}}{1 + \left( \frac{\beta_n}{\beta_p} \right)^{1/2}}$$

(3)

an region 3, both transistors are in saturation. they act a current source, the equivalent circuit, in this region as shown in fig.

This region 3 is Very unstable and change over from one logic level to other.

If  $V_{in} = -V_{tp}$ ,  $\beta_{p} = \beta_{n}$ , equation reduces to  $V_{in} = 0.5 \text{ VDD}$ At this Point two 'p' factors will be equal.

$P_n = P_p$ , the device geometries should satisfy  $\frac{u_n w_n}{L_n} = \frac{\lambda l_p w_p}{L_p}$

The mobilities of electrons and holes are unequal.

It is necessary that the width to length ratio (w/L) of p-device be two to three times that of n-device i.e

$$\frac{\omega_{P}}{\psi} = 2 \cdot \frac{\omega_{n}}{L_{n}}$$

By keeping minimum size geometries for both p-and n-devices, effect 'B' ratio is minimized.

The transfer characteristics as shown in Ag.

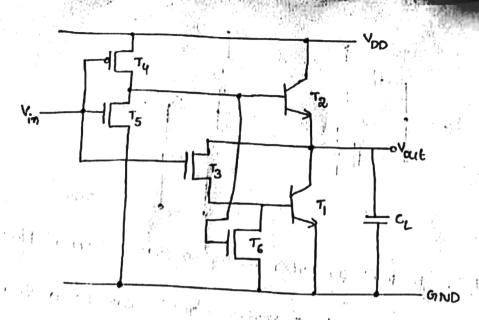

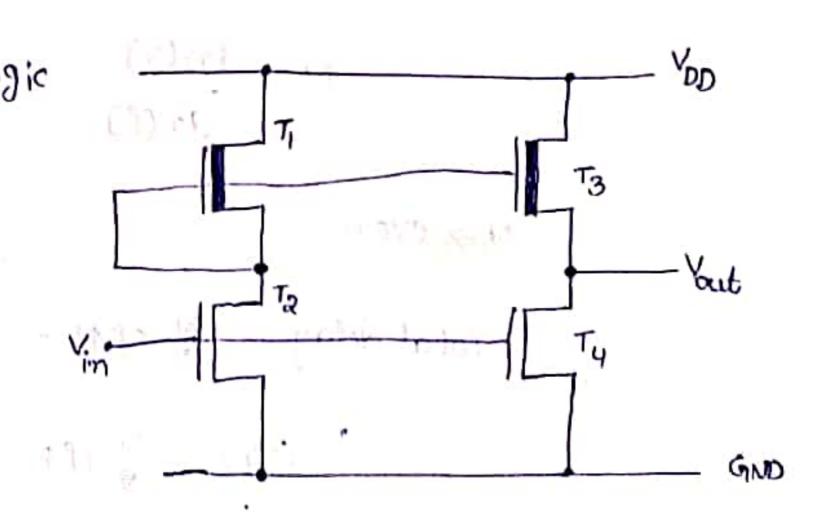

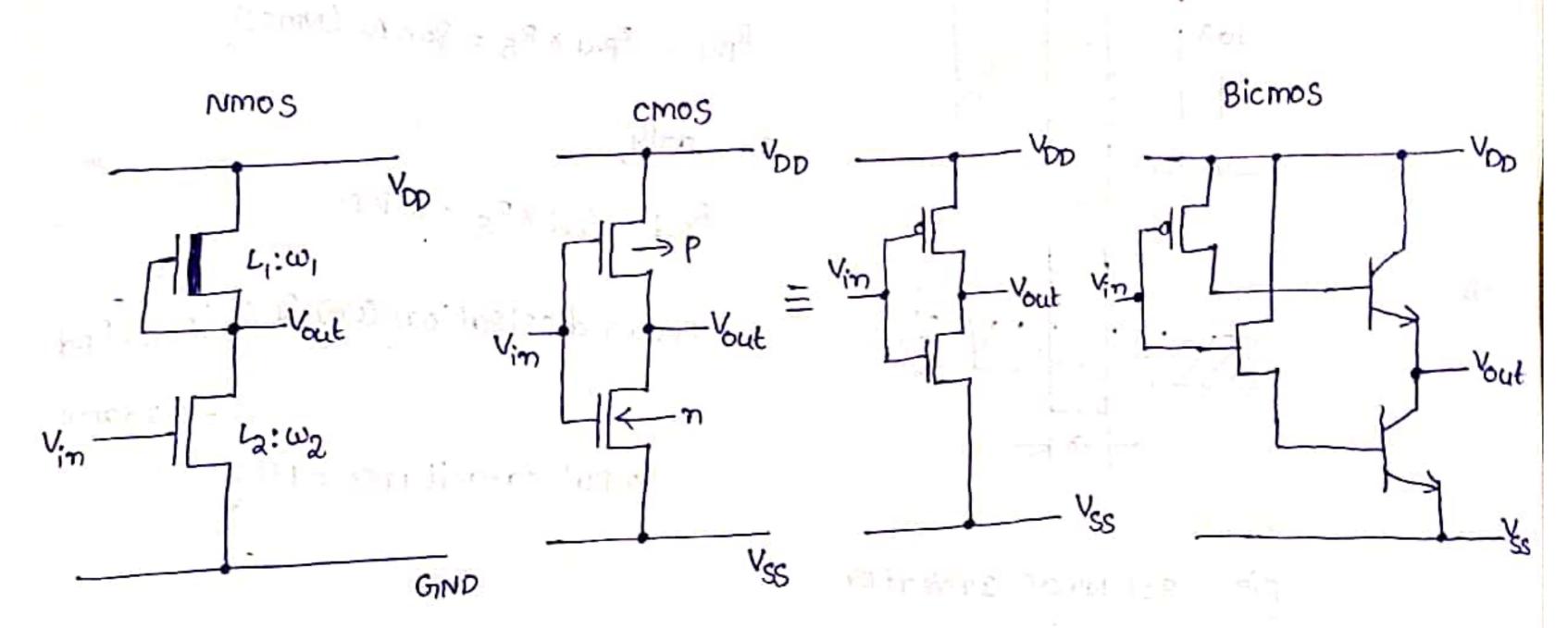

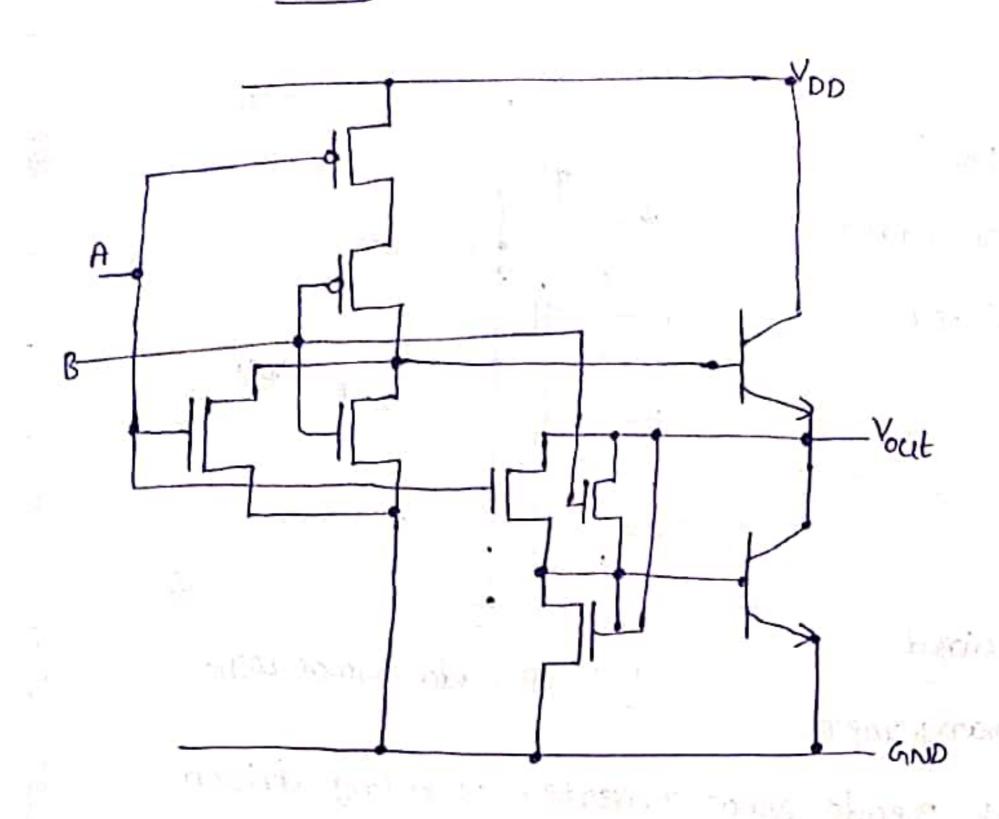

#### Bicmos Inverter:-

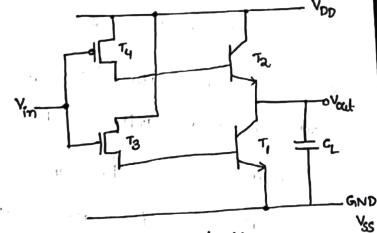

The simple Bicmos Inverter as shown in fig. below

The Inverter circuit

consists of two bipolar transistors

Ti, Ta and mos devices are

enhancement mode.

operation

\* Vin=0 ive Logico, Is is off which keeps T, non-conducting.

Ty is on and supplies base current to To which conducts and act as a current source to charge the load of toward +5v(VDD). The output but goes +5v less the base to emitter drop YBE of To.

\* Vin = Logic 1 (+5v), Ty is OFF so that To will be non-conducting.

To is on and supplies current to base of To which conducts

- through it to 'o' volts (OIND). The Yout falls to 0 volts plus the saturation voltage VE(sat) between collector and emitter of Ti.

- \* charging and discharging of the load c<sub>L</sub> is very fast because transistors T<sub>1</sub>, T<sub>2</sub> present low Impedances when turned on into saturation.

- Yee (sat) is quite small and Yze equals 0.7 volts approximately.

- The Inverter offers a low output Impedance and a high Input Impedance. It occupies a relatively small area but has a high current drive capability.

- There is a constant Dic path between the rails through T3 and which allows a significant static current flow whenever Vin=Logic

There is another problem, that there is no discharge path for current from the base of either npn transistor when it is turned off. This effects the speed of action of the circuit.

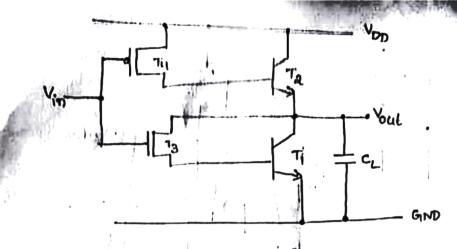

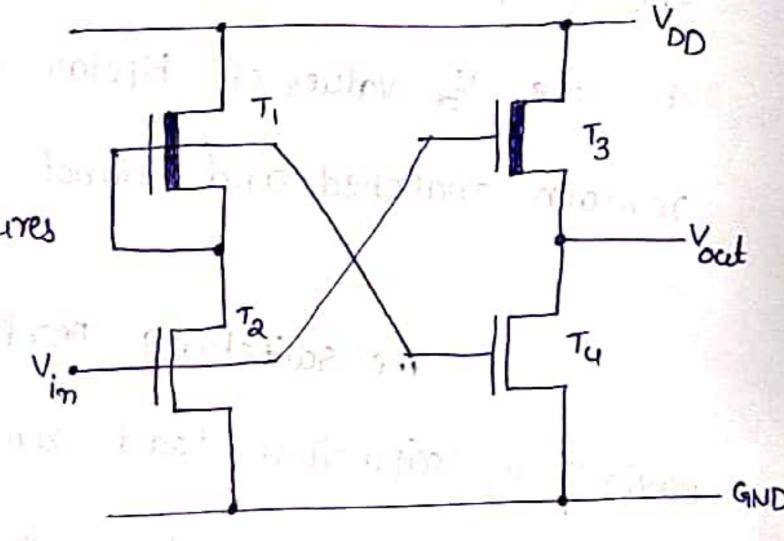

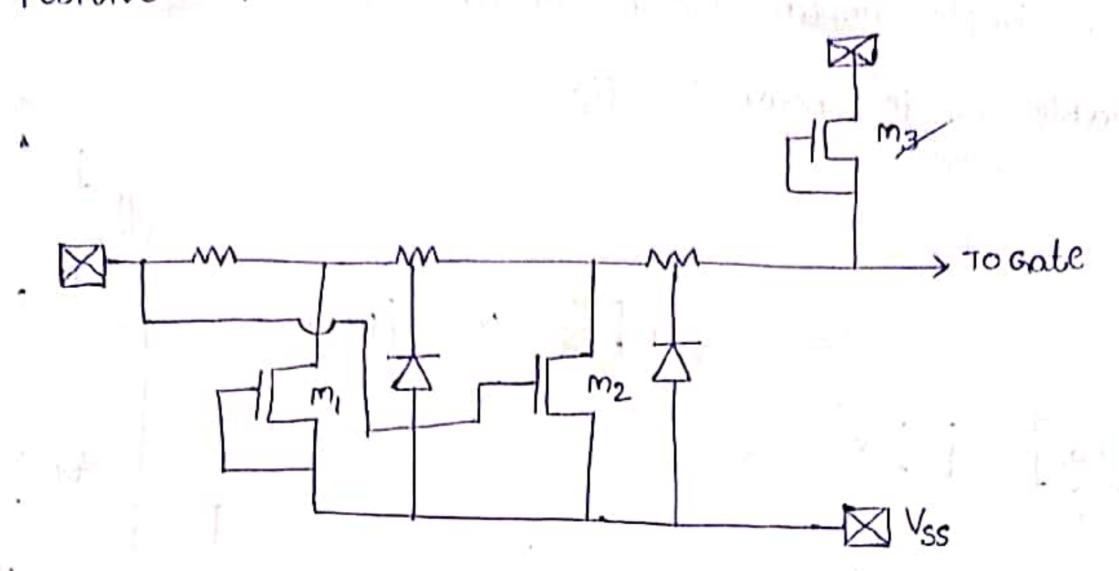

in an Improved Inverter circuit, as shown in fig.

Fig: - Bicmos Inverter with no static current flow

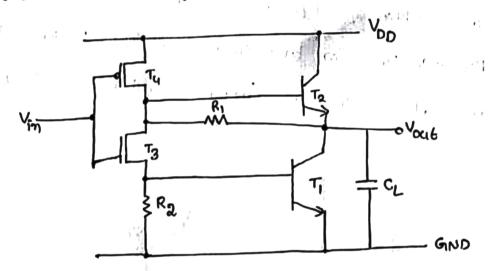

resistors as shown in fig.

The resistors provide an Improved swing of output Voltage when either bipolar transistor is off.

They also Provide discharge Paths for the base currents during turn-off An Improved Bicmos Inverter using mos transistors for base current discharge as shown in fig.

turned off. That is when  $T_2$  is to be turned off,  $T_5$  gets turned on and provides discharge Path for base current of  $T_2$ . Bicmos Invertous are more suitable where high load current sinking & sourcing is required.

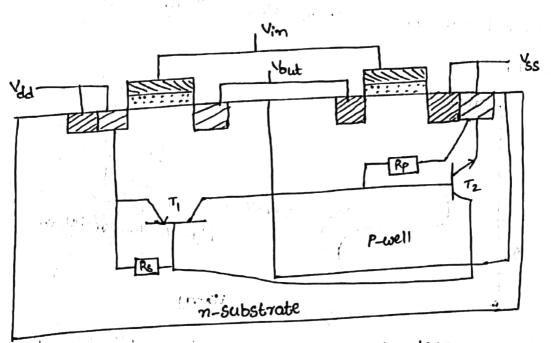

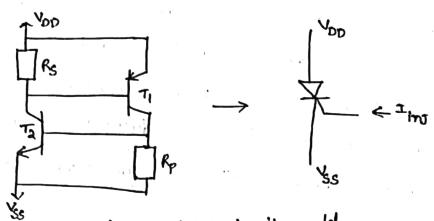

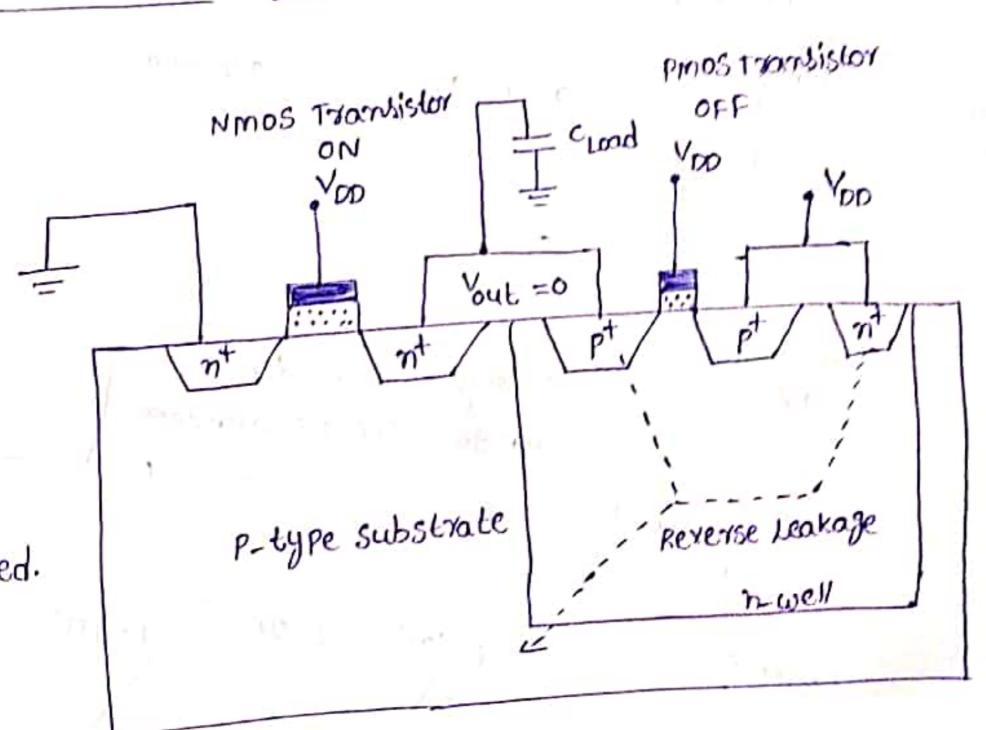

- A problem which is Inherent in the P-well, n-well process is due to large no of Junctions, which are formed in these structures, consequent presence of parasitic transistors and diodes.

- the establishment of low resistance conducting Path between VDD, VSS.

- -> Latch-up may be Induced by glitches on supply rails (07) Incident radiations.

consider, Parasitic components associated with the p-well structure,

Fig: - Latch up effect in P-well structure

- between VDD, Vss.

- Tf Sufficient substrate current flows to generate enough voltage across Rs to turn on transistor T, this will then draw current through Rf

- If voltage developed is sufficient, To also turn on, establishing

- a self sustaining www resistance Path between supply rails.

- If a current gains of a transistors BxB2>1, Latch up may occur.

- Equivalent circuit as

Fig: Latch up circuit model.

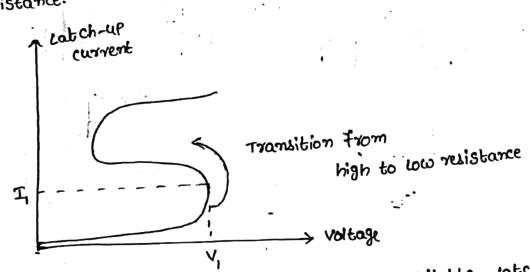

→ with no Injected current, Parasitic transistors exhibit high resistance, but sufficient substrate current flow will cause switching to Low resistance.

once catched up, this condition maintain until the catch-up current drops below II.

Remedies for Latch-up Problem Include,

- \* Increase in substrate doping levels with a consequent drop in value

- \* Reducing Rp by control of fabrication parameters and by ensuring Low contact resistance to Yss.

### \* Introducing guard rings

Latch-up in N-well fabrication as shown in fig.

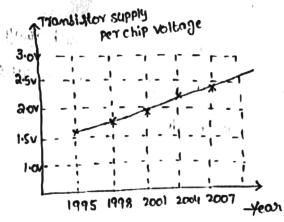

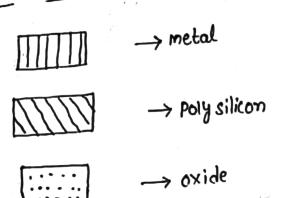

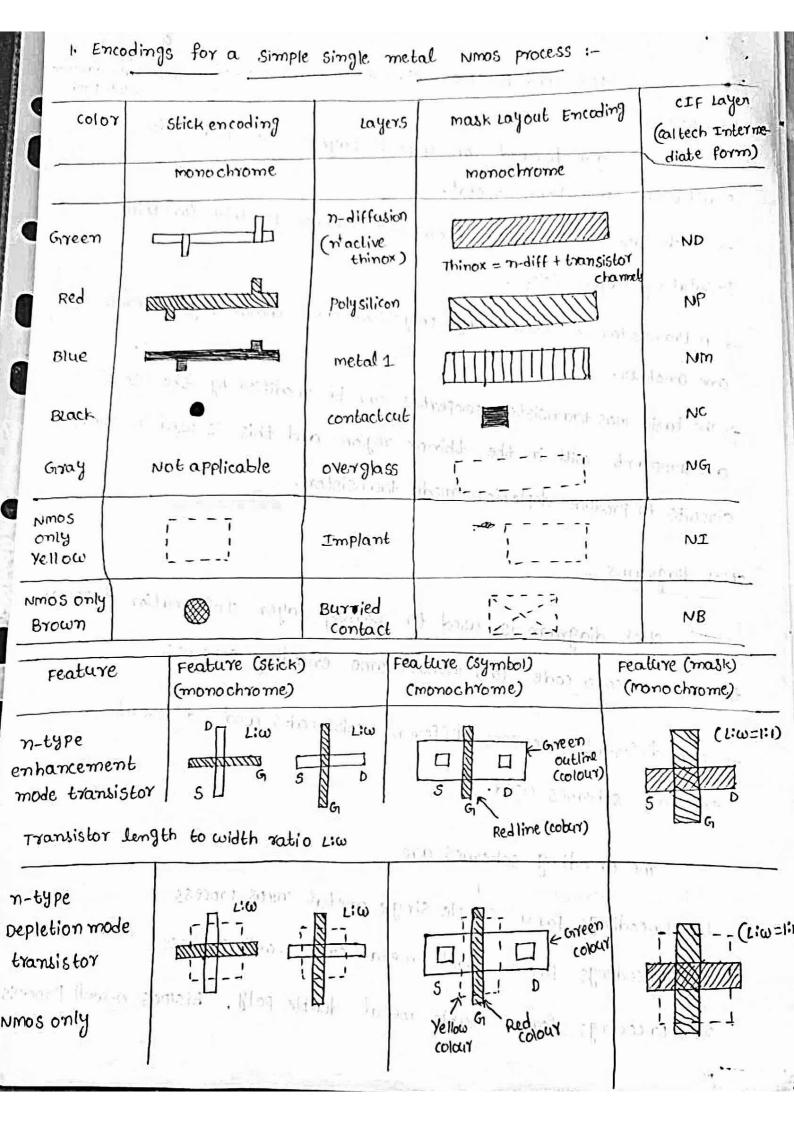

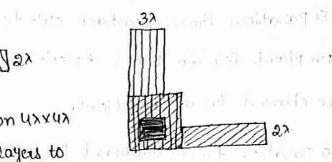

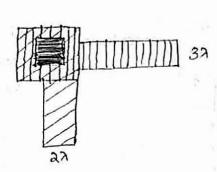

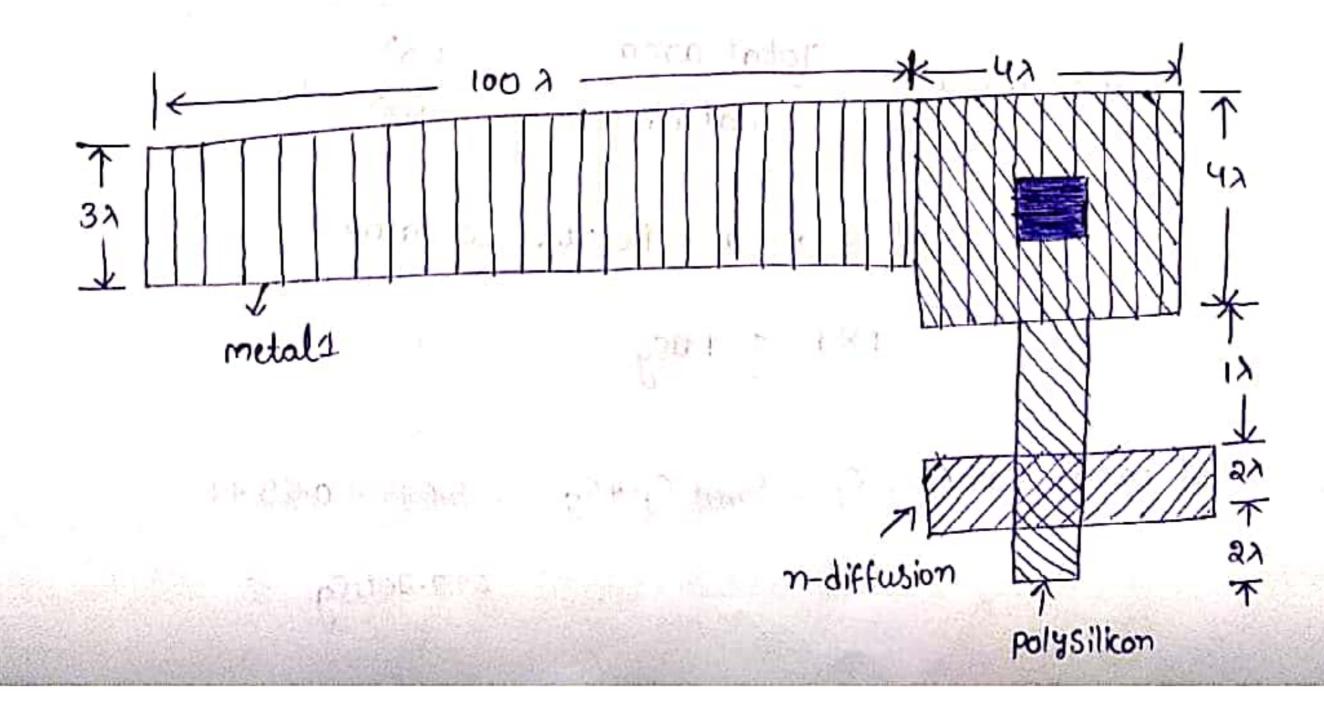

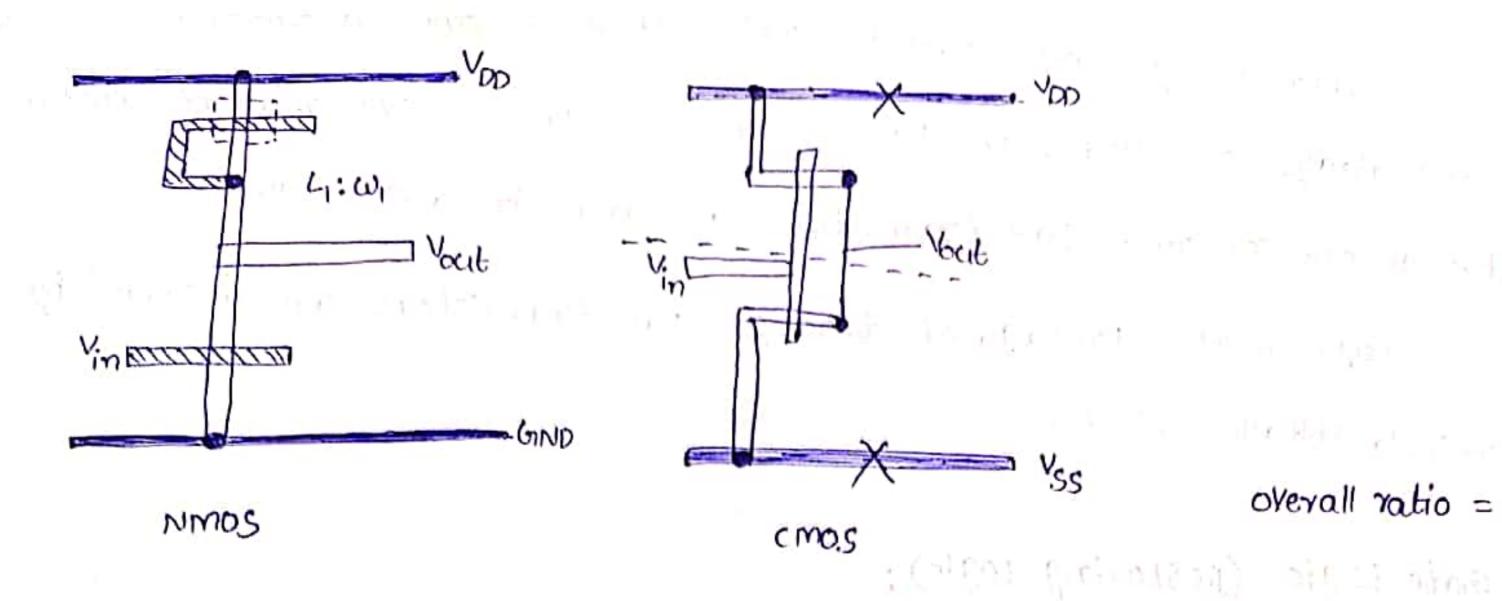

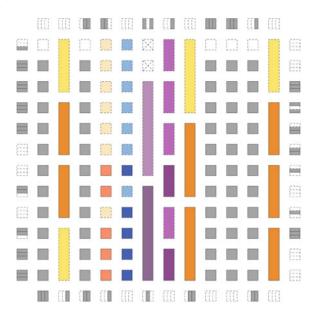

#### mos layers :-

Mos circuits are formed on 4-basic Layers i.e. n-diffusion, p-diffusion, polysilicon, metal.

- > Each layer is Isolated from one another by thick (or) thin Insulating layers (sion).

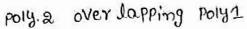

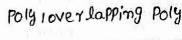

- > A transistor is formed by polysilican and thinox regions cross one another.

- The basic mos transistor properties can be modified by the use of an Implant with in the thinox region and this is used in moss circuits to produce depletion mode transistors.

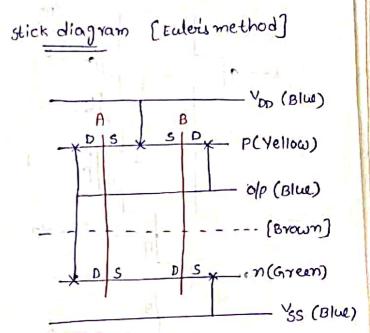

#### stick diagrams :-

stick diagram is used to convey layer Information through the use of color code (or) monochrome encoding schemes.

terplanat.

was older at house defence radiagnet

39 K.F.

maker to and store

-> For different processes different color codes and different encoding schemes used.

The encoding schemes are

(minima) well know

- 1. Encodings for a simple single metal mmos process

- 2. Encodings for a Double metal cmos p-well process

- 3. Encodings for a double metal double poly, Bicmos n-well Proce

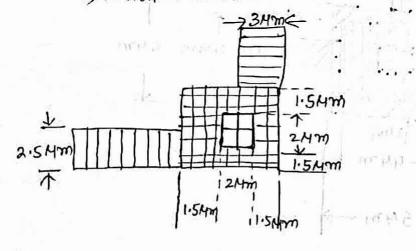

Note: P-type transistor are placed above and n-type transistors below the demarcation line.

Bicmos n-well Process

|                                       |                        |                                  | 1 2017                                                                       | mask layout encoding                   | 100                          |

|---------------------------------------|------------------------|----------------------------------|------------------------------------------------------------------------------|----------------------------------------|------------------------------|

| color                                 | stick discoding        |                                  | Layers                                                                       |                                        | 6 49                         |

| orange.                               | mono chrome            |                                  | Polysilicon                                                                  | 2 Milli                                | cPS and                      |

| Pink Pale Green                       | Not separately encoded |                                  | P-base of Bipolar npr transistor Burried collector of Bipolar npr transistor | maell 1                                | CBA<br>Not offi<br>-co       |

| Feature                               | (                      | Feature (Stick)<br>Cmono chrome) | 1                                                                            | conochrome)                            | Feature (mask<br>Cmonochrome |

| type embancement                      |                        | Demarcation lines                | Δ:ω                                                                          | 5 D ovarge                             | 5 G                          |

| type enhancement<br>bly. a transistor |                        | Demarcati                        | Revelent                                                                     | orange                                 | S G                          |

| nph bipolan transistor                |                        |                                  | 9/6/ (Yai 2.5 r m ect.)                                                      | harmanad<br>Impuranad<br>Valaborati ak |                              |

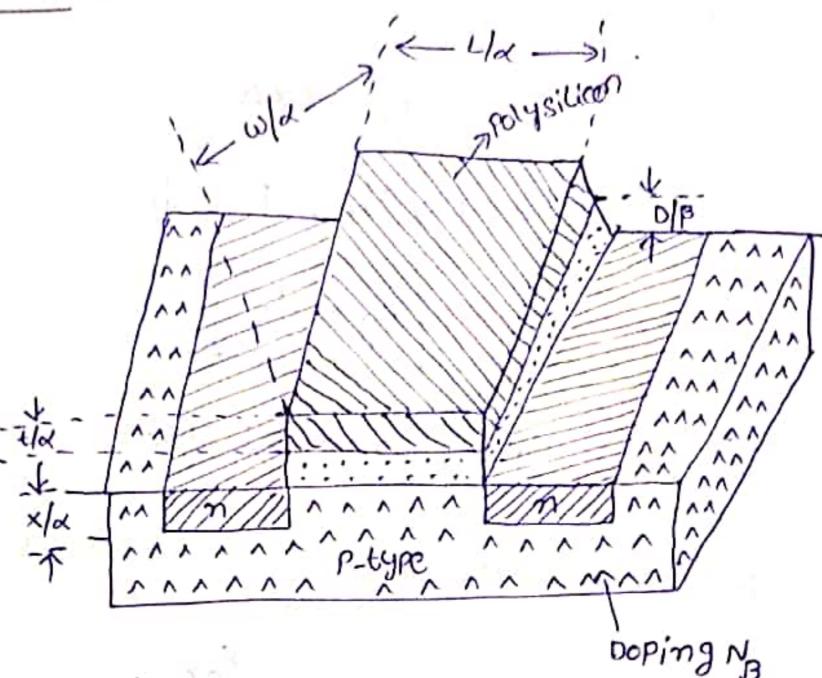

## Design rules and Layout:

The design rules are the effective Interface between the circuit/system designer and the fabrication engineer.

circuit designers in general want tighter, smaller layouts for Improved performance and decreased silkon area.

on other hand, the process designer wants design rules that result in a controllable and reproducible process. worl colloring

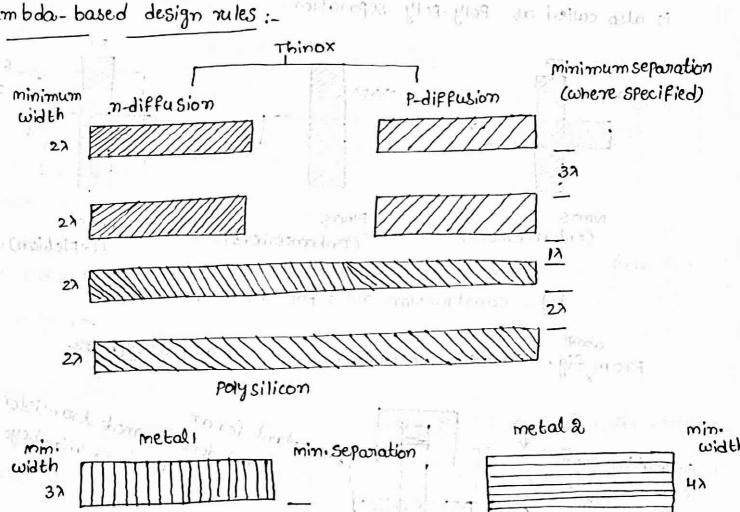

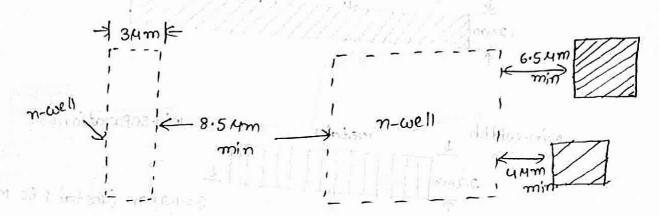

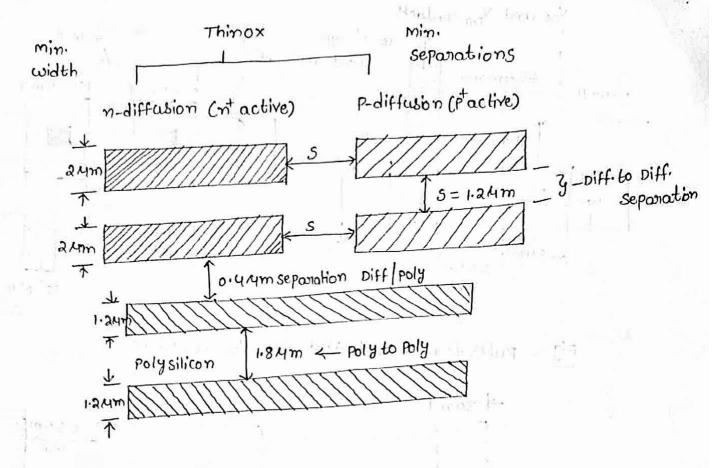

Lambda-based design rules:

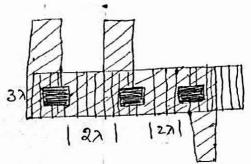

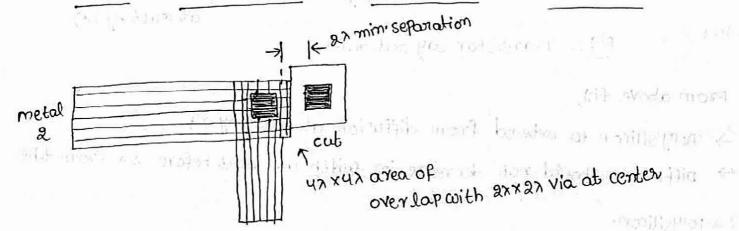

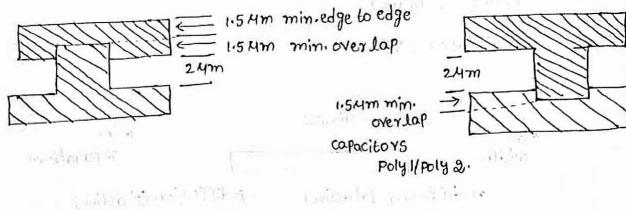

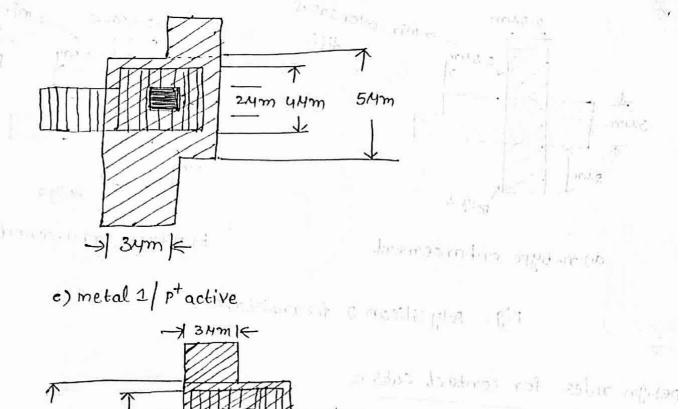

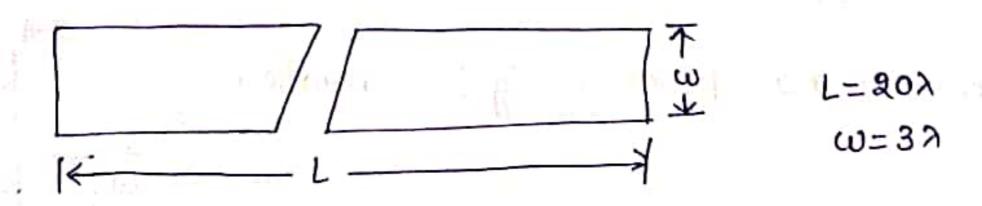

design rules for wires (nmos and cmos)

- > From above fig,

> minimum nt-diffusion and pt-diffusion width is 27

- -> minimum spacing between two nt-diffusion and pt-diffusion is 32

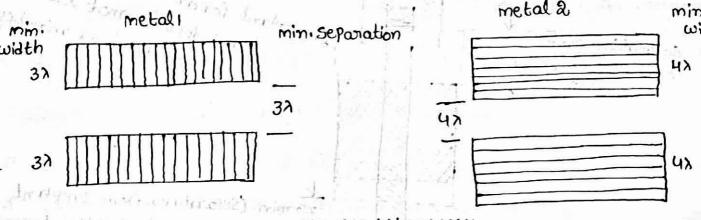

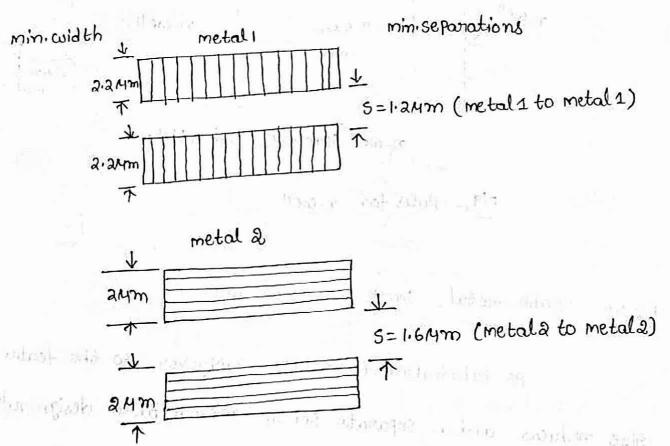

- > For metal 1, minimum width should be 32 and minimum separation from another metal 1 wire is 32.

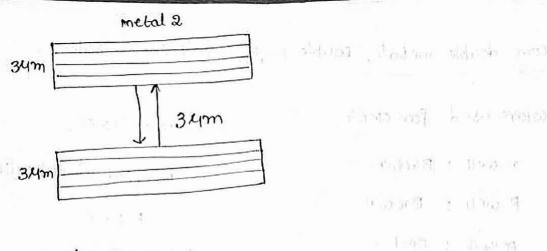

- > For metal 2, minimum width should be ux and minimum separation from another metal 2 wire is ux.

- For Polysilicon wire the minimum width is 27 and minimum separation from another Polysilicon wire is 27. This separation is also called as Poly-poly separation.

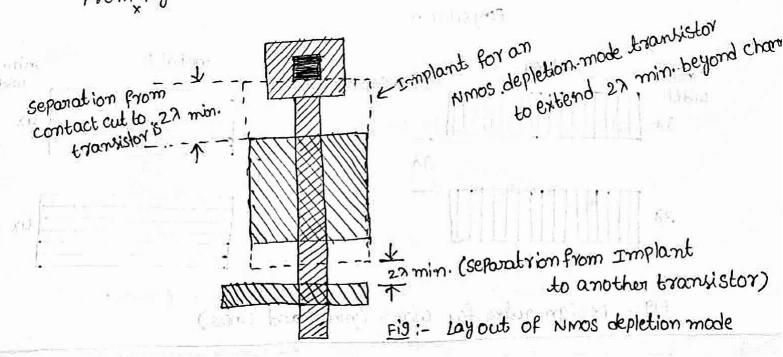

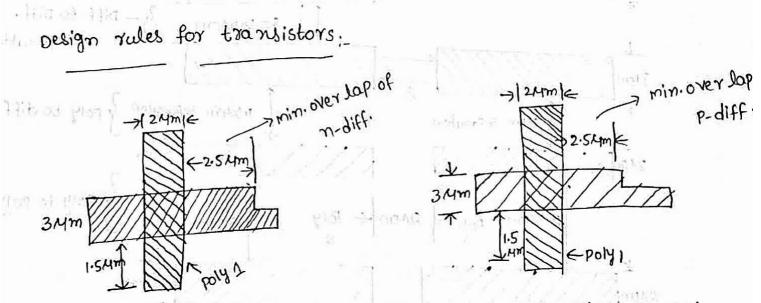

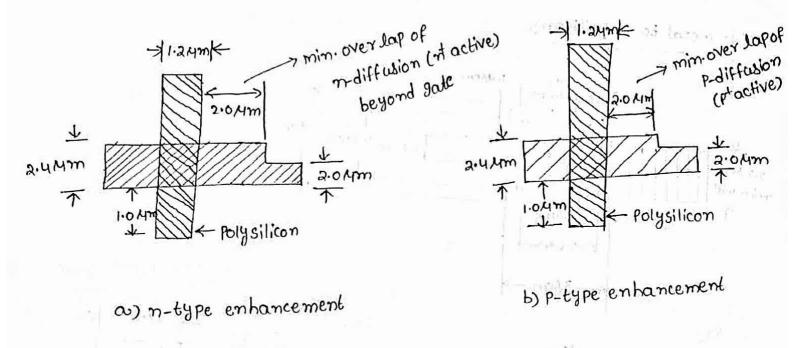

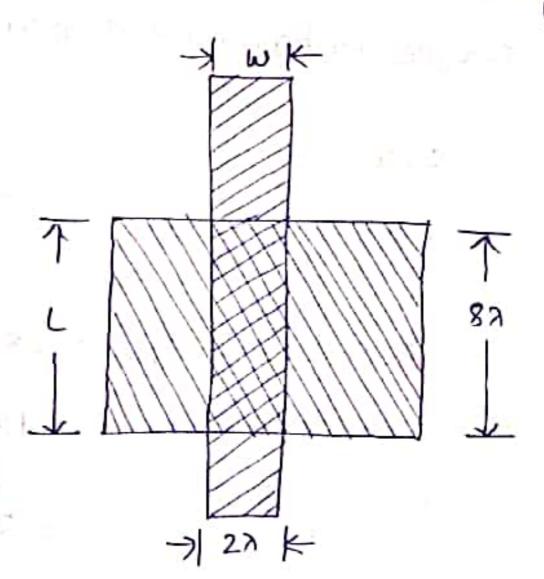

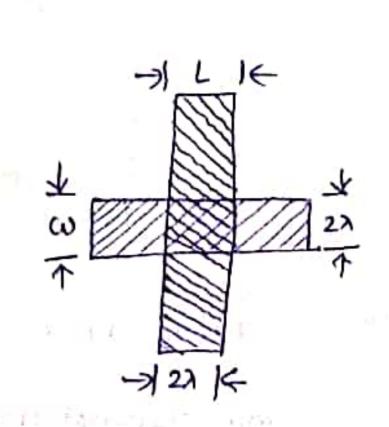

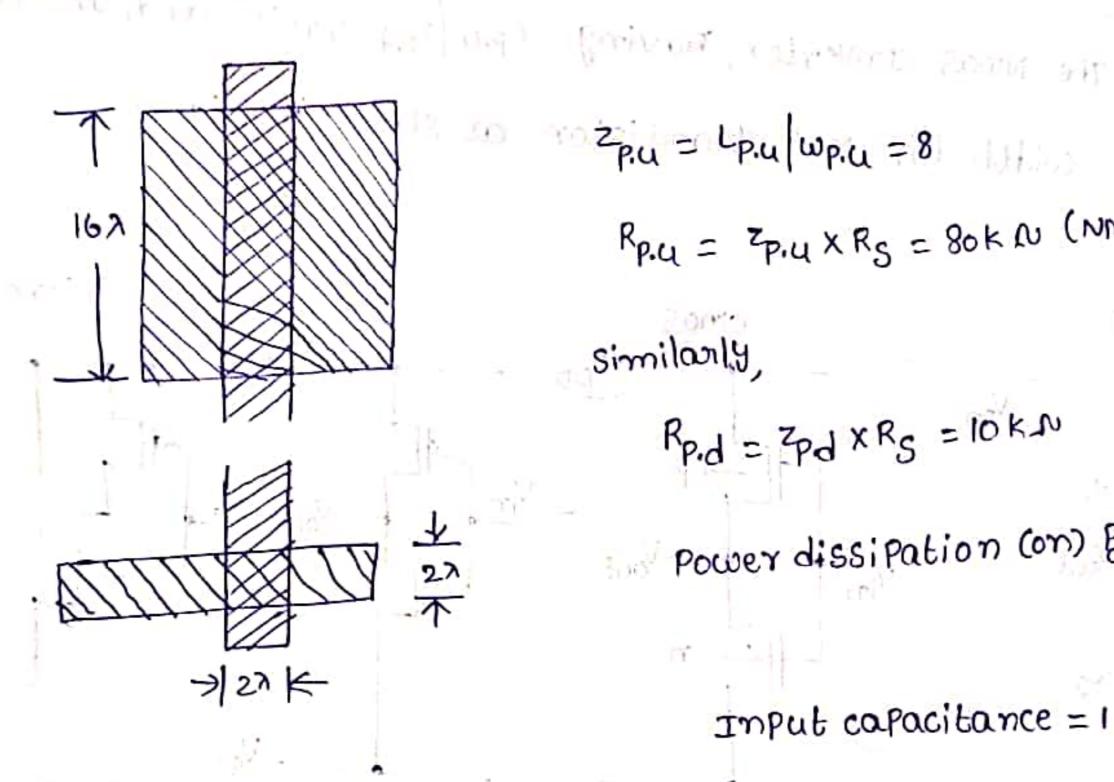

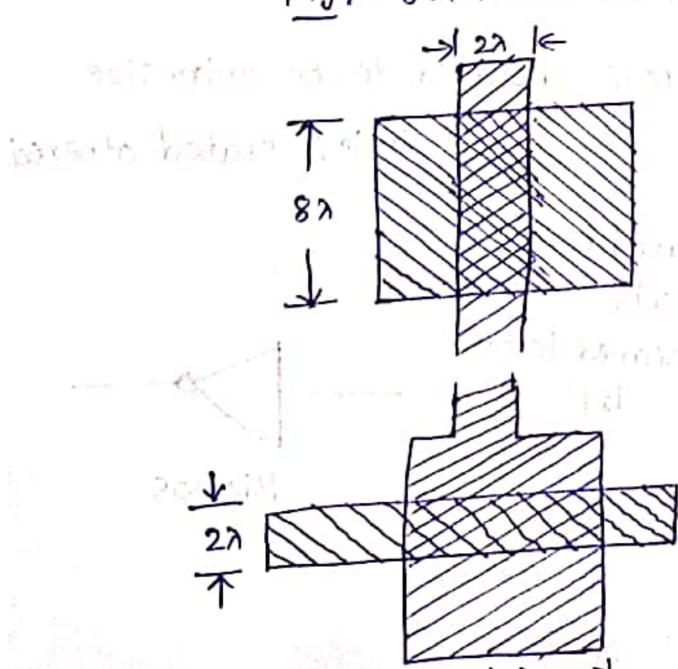

Fig: construction rules for transistors

From fig. smallest transister width 22 and length 27.

From above figure,

- Separation from contact cut to transistor is an

- Implant for an NMOS depletion mode transistor has extend ax from the channel in all directions.

- separation from Implant to another transistor is an. ->

व ने प्रतिक्रिक वर्ष १ वर्ष व व १ वर्षाल

(polysilicon to extend from diffusion at least by 22)

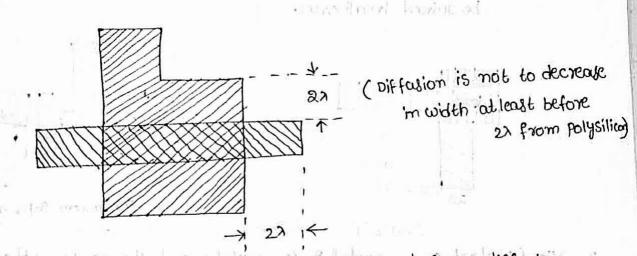

Fig: - Transistor Lay out rules

From above fig,

- > Polysilican to extend from diffusion at least by 22

- → Diffusion should not decrease in width at least before 22 from the Polysilicon.

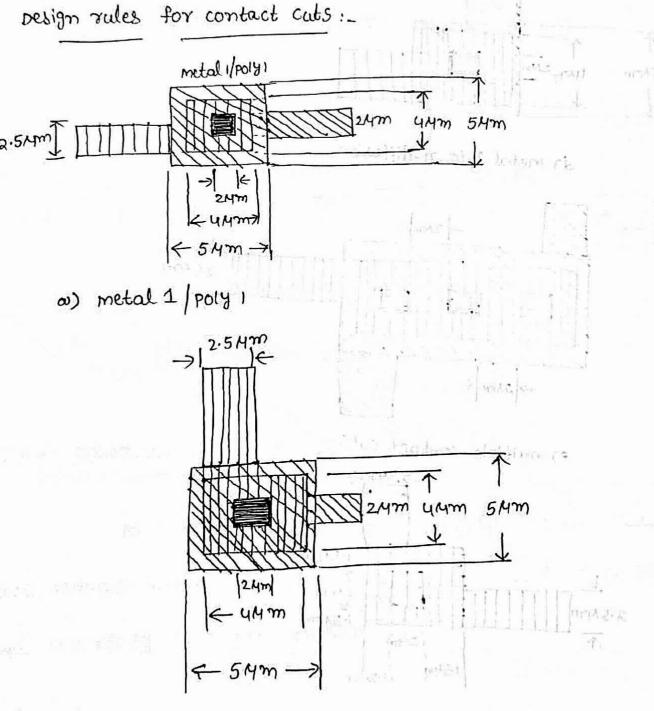

contact cuts:

when making contacts between Polysilicon and diffusion in mmos circuits it should be recognized that there are 3 possible approache

- 1. Polysilicon to metal and then metal to diffusion

- Burried contact (Poly to diffusion)

- Butting contact (Poly to diffusion using metal)

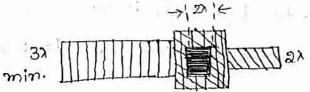

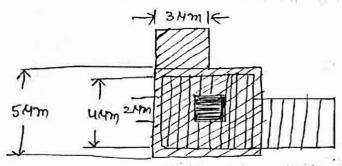

# metal 1 to Polysilicon (or) to diffusion :-

2xxx ad centered on uxxux Superimposed areas of layers to be joined in all cases.

minimum separation multiple cuts

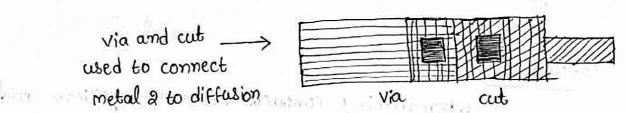

#### via (contact from metal & to metal 1 and thence to other layers)

via and cut used to connect

Fig: - Design rules for wives (nmos and cmos) con contacts (nmos crockettin to believe made been dodate out and inglished of cmos

de Burried comback (not) to diffusion)

3. Bubling contact (101) to difference wing notified - 3.

Fig: Design rules for wires (24m cmos)

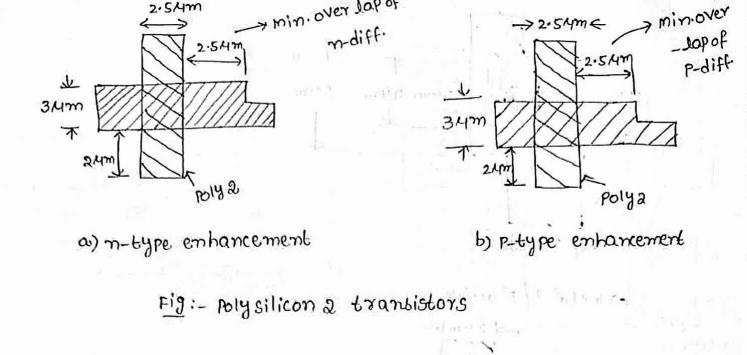

a) n-type enhancement

b) p-type enhancement

Fig: Polysilicon 1 transistors

b) metal 1 to poly 2 190 I ladon of ()

d) metal 1 to n-diffusion

e) multiple contact cuts

f) via metal 2 metal 2 de la la la de de

Fig: Rules for n-well and YDD, Vss contacts

& Inton

features.

n-well spacings and width

Fig: Rules for n-well

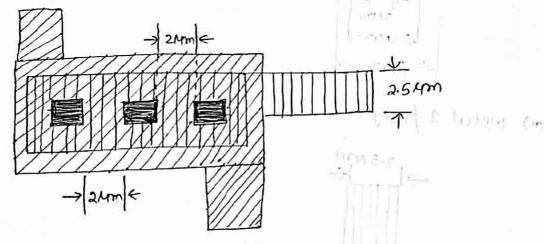

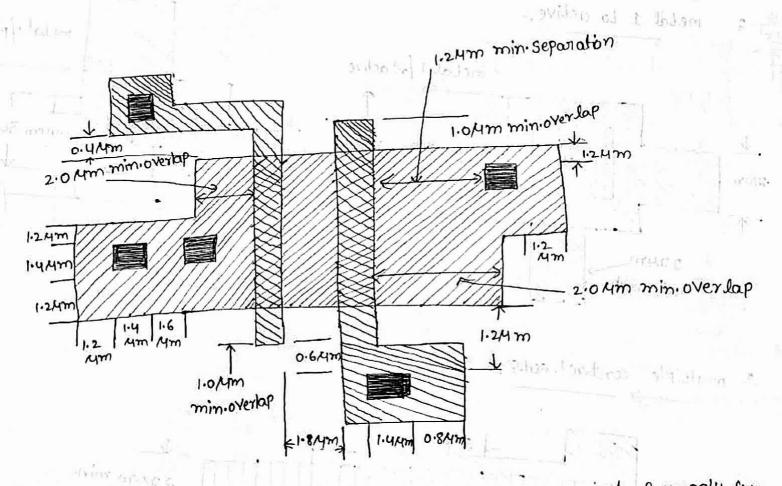

1.2 4m Double metal, single poly. cmos rules:

As fabrication technology, Improves so the feature size reduces and a separate set of micron tased design rules must accompany each new feature size.

Fig: Design rules for wires (Interconnects)

W

Bills to combutte

Fig: - All devices shown in n-type. The same rules for apply for P-type

Miller

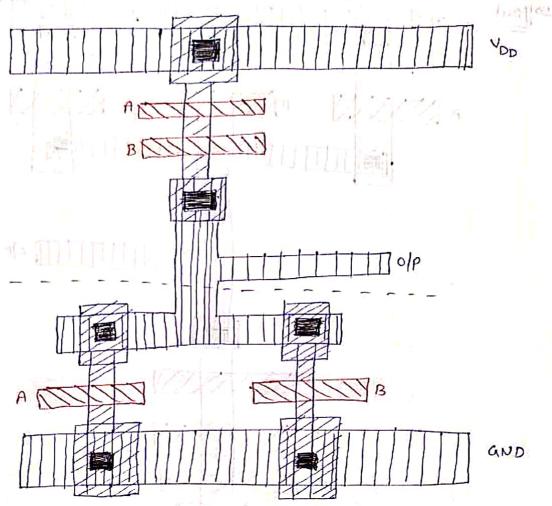

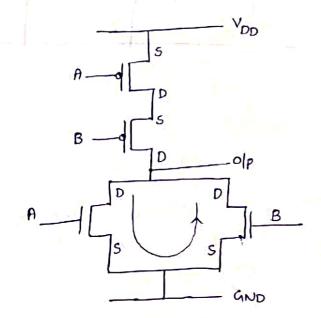

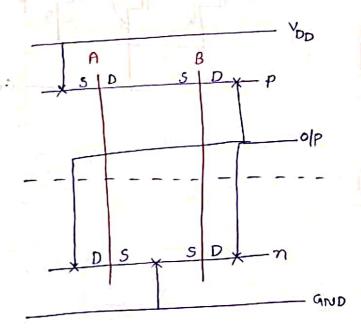

1. Draw the stick diagram and layout diagram of NMOS Inverter.

MELTY or Layout: -VDD g - Flandam of

11 345 056

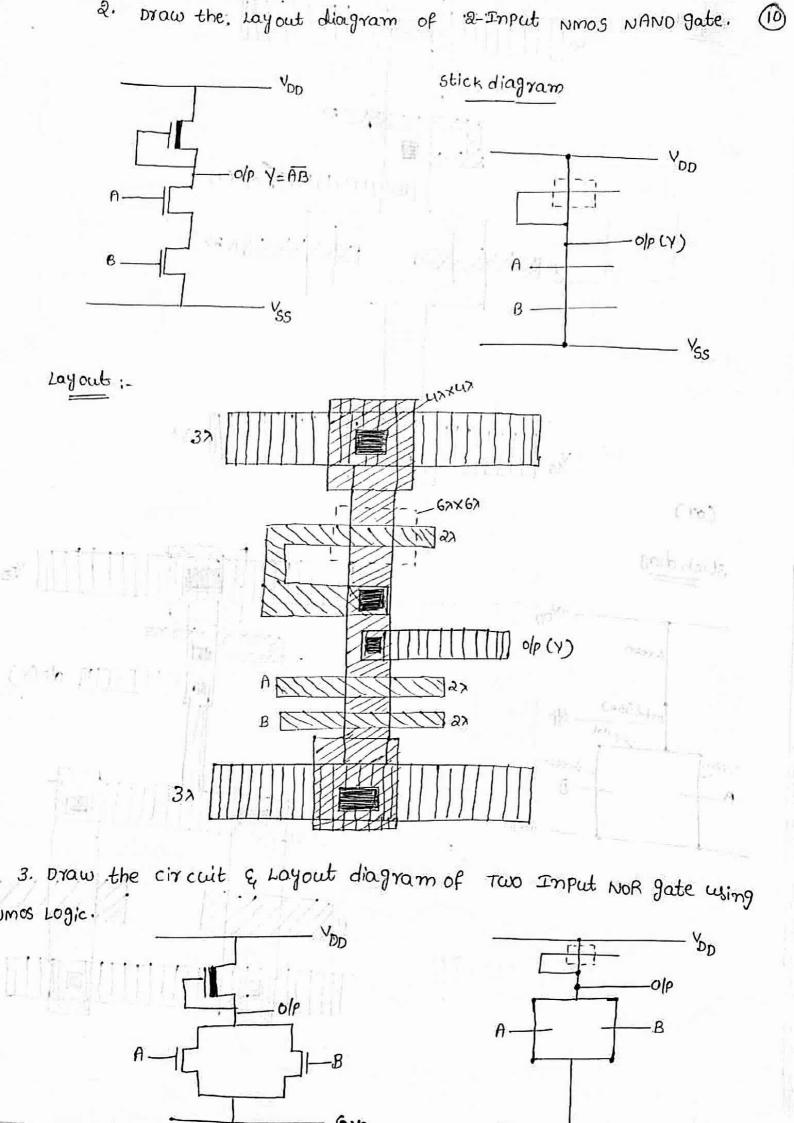

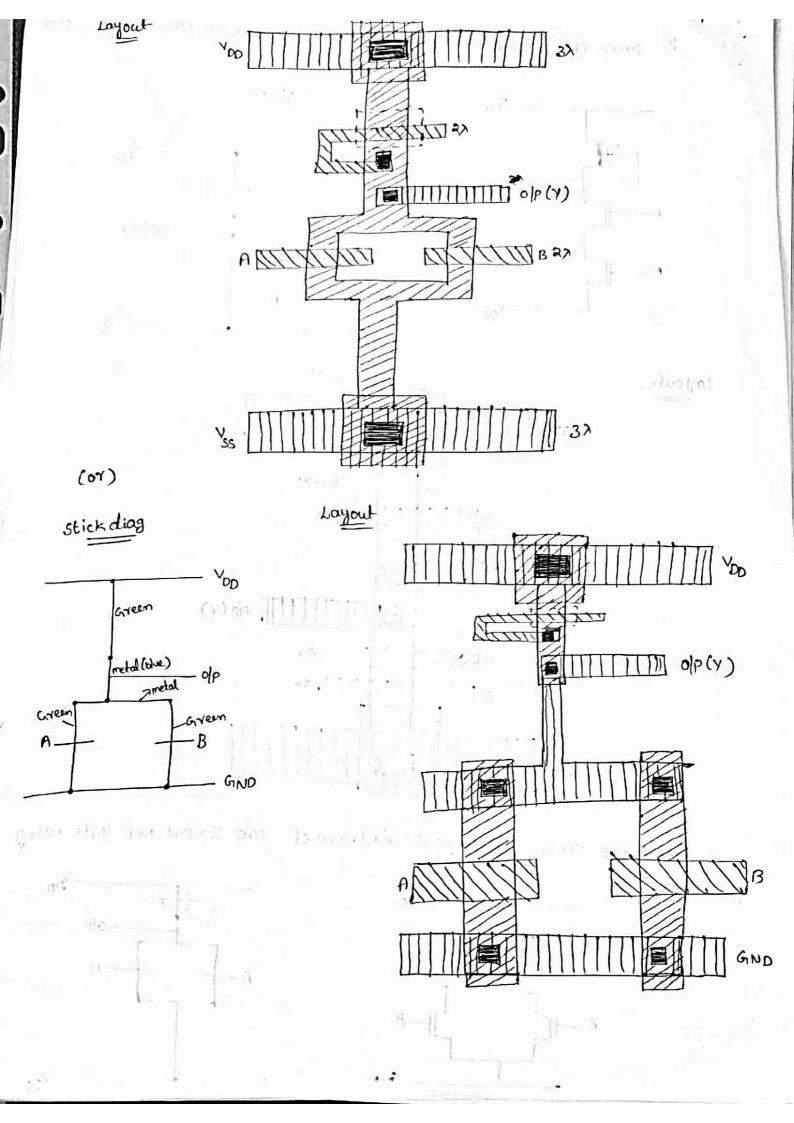

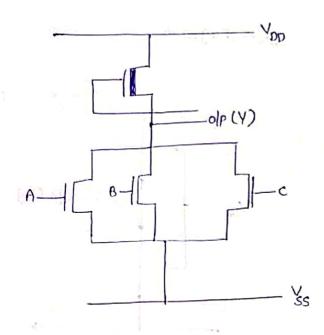

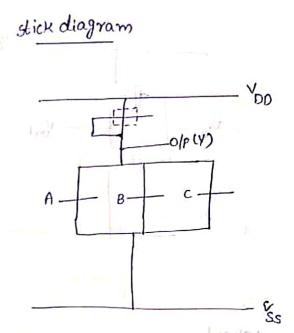

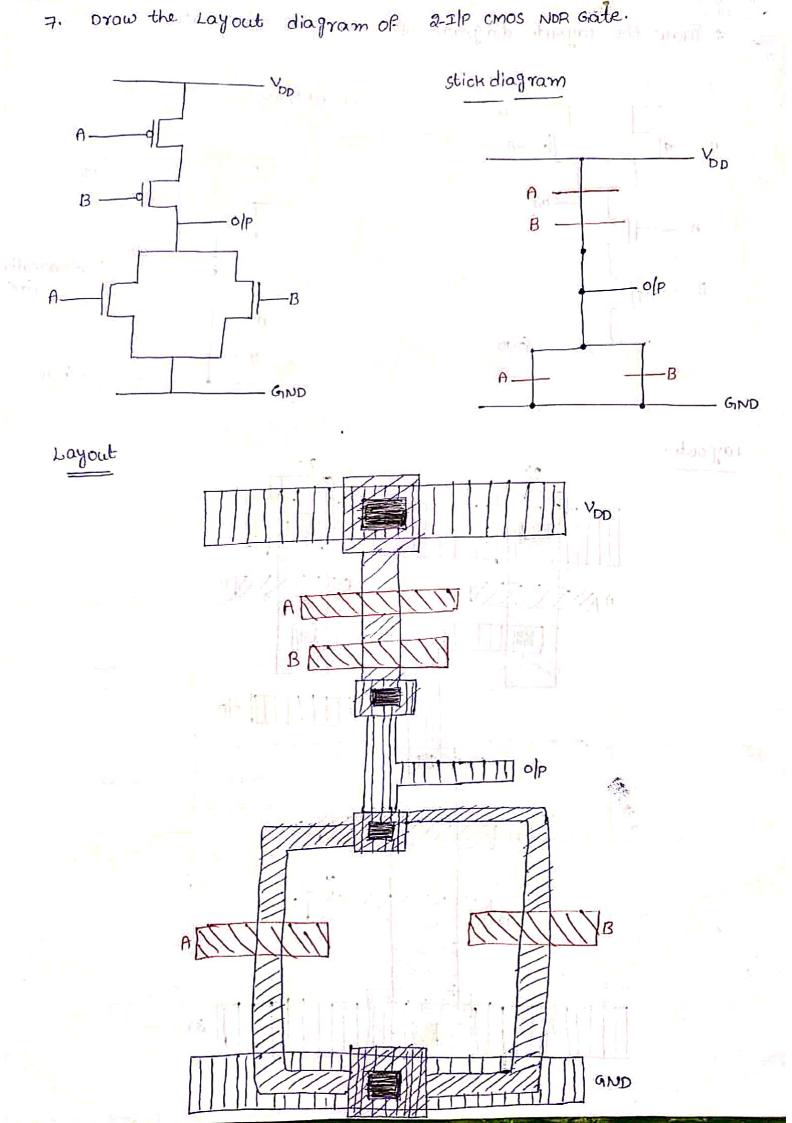

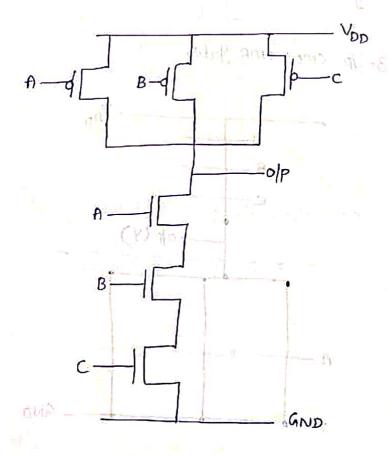

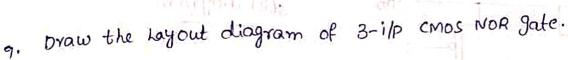

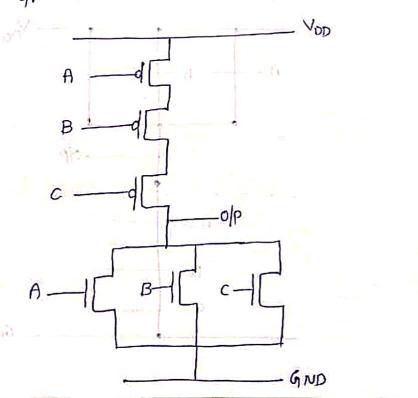

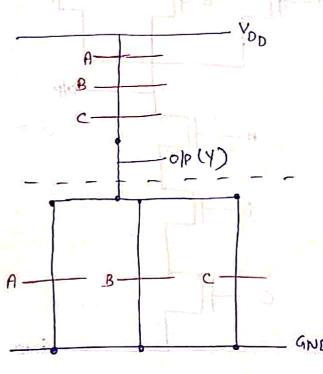

# 4. Draw the Layout & stick diagram of 3-ilp NOR gate.

Loyout

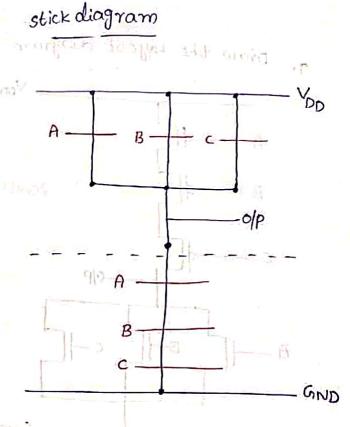

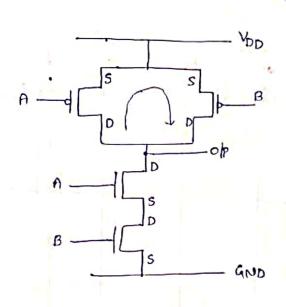

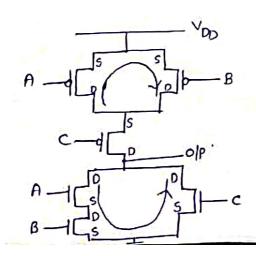

# 5. Draw the stick and layout diagrams of cmos Inverter.

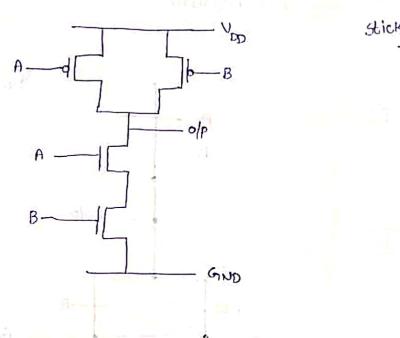

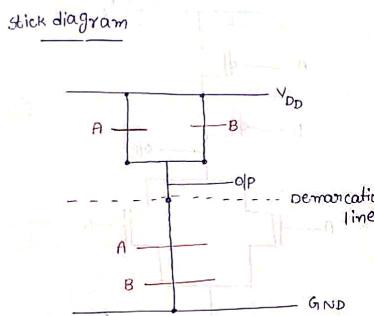

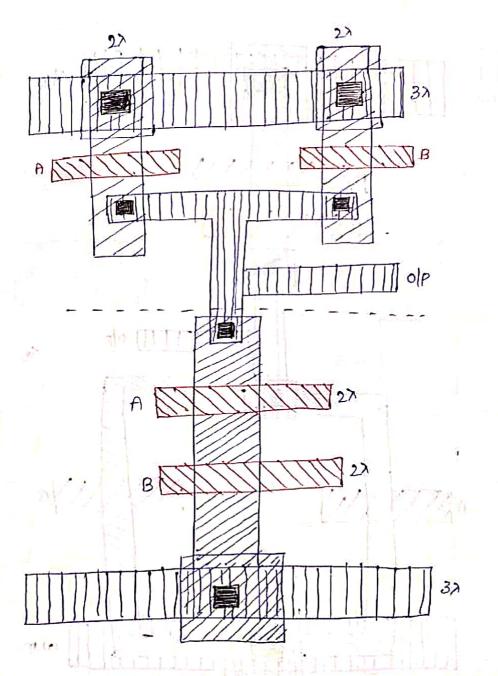

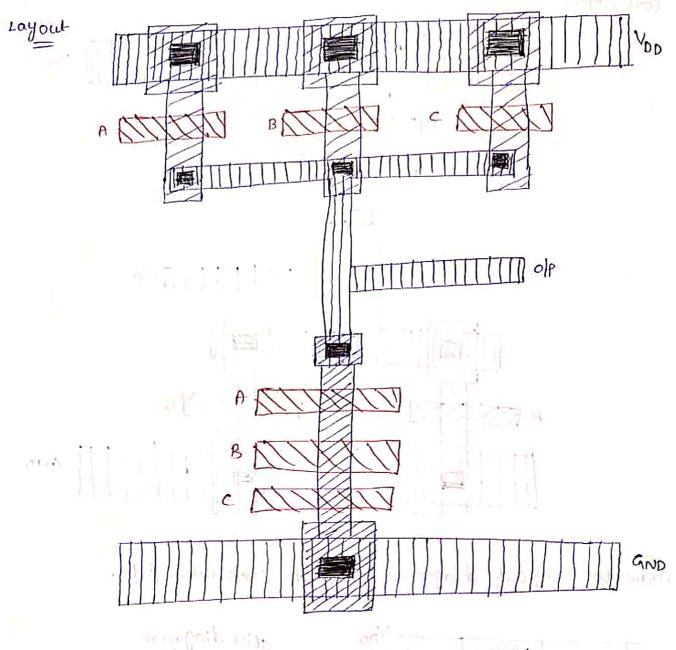

6 Draw the Layout diagram of 2-I/P cmas NAND Grate

Looper

lay out :-

(or) Layout

8. Draw the Layout diagram of 3-Ilp cms NAND gate.

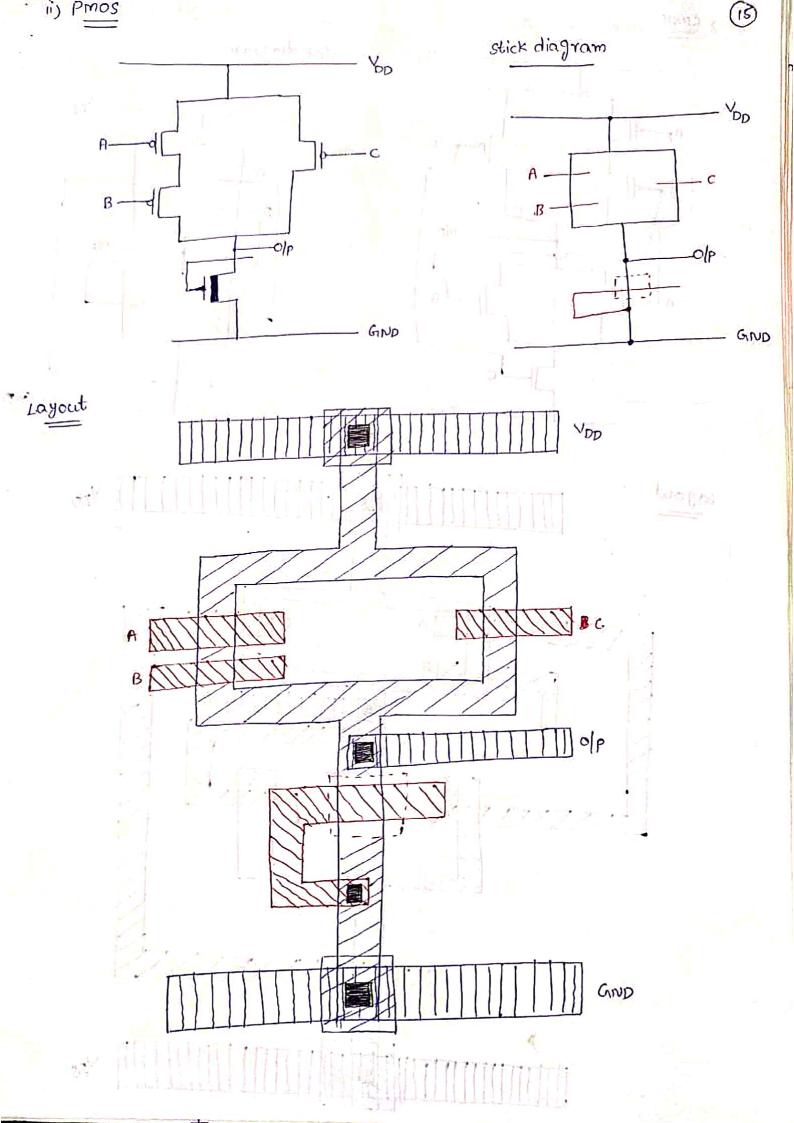

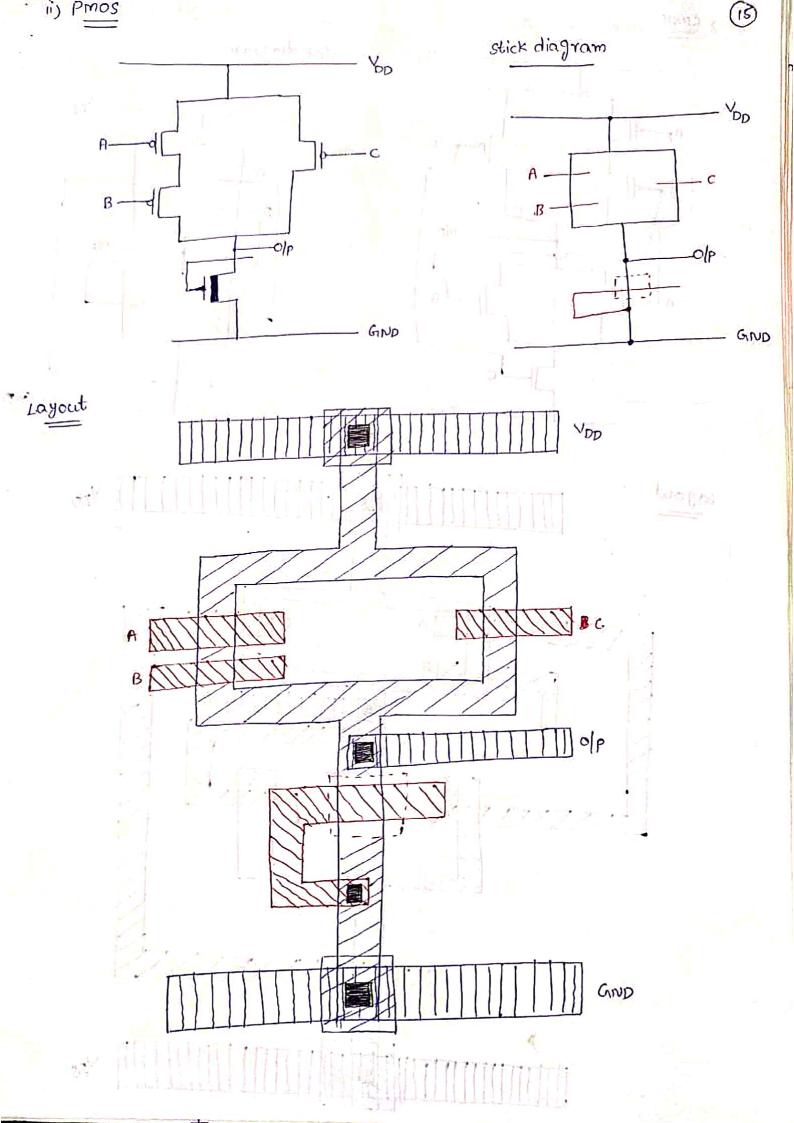

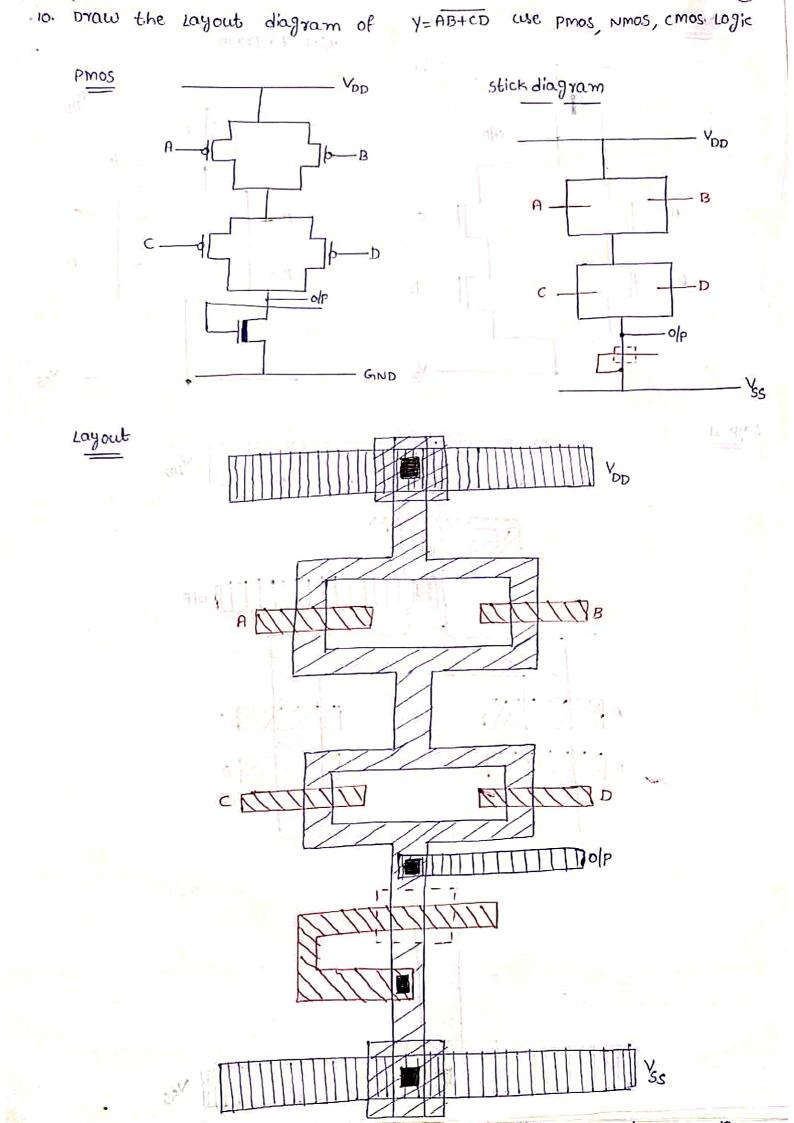

lo. Draw the Layout diagrams of Nmos, Pmos, cmos using Expression Y=(A+B)C

.

stickdiagram V<sub>DD</sub> A D D -olp Vss

Draw the Stick diagram of 2-Input cmos NAND gate.

Draw the stick diagram of 2-Ilp cmos NOR gale.

\* Y=a·b+c we cmos.

Y= a (b+c+d) -> Draw the Stick diagram of stick diogram b C a 5 D 0/1

# Basic Circuit concepts

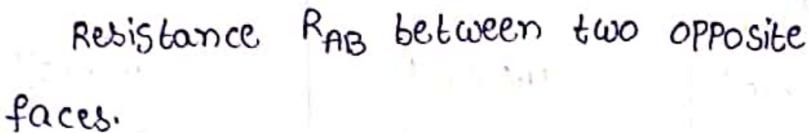

sheet resistance (Rs):-

sheet resistance is a measure of resistance of a thin films

that have a uniform thickness.

consider a uniform slab of conducting material of resisitivity'e', width 'w', thick ness 't', length'L'.

Fig: - Sheet resistance model

where A -> Area of cross section

$$R_{AB} = \frac{PL}{tw}$$

ohm

consider L=w, since it is a uniform slab,

$$R_{AB} = \frac{PL}{tL} = \frac{e}{t} = R_{S}$$

The sheet resistance  $R_S = \frac{P}{t}$  ohm/square

For Example, 14m Per side square slab of the material has exactly same resistance as a 1cm per side square slab of the same material if the thickness is same.

Typical sheet resistance Rs of mos Layers for 54m, orbit 24m, The Court of the C orbit 1.24m is given in table.

| Layers                | Rs ohm per soucare |                       |                          |

|-----------------------|--------------------|-----------------------|--------------------------|

|                       | 5 km               | orbit aum             | orbit I.a.um             |

| metal                 | 0.03               | 0.04                  | 0.04                     |

| Diffusion (or active) | 10-750             | 20->45                | 20->45                   |

| slizide               | <b>2</b> →4        | Special States to the | . July or ( Till a hards |

| Polysilicon           | 15→100             | 15 → 30               | 15→30                    |

| n-transistor channel  | 104                | 2×104                 | 2×104                    |

| p-transistor channel  | 2.5 x 104          | 4.5 × 104             | 4.5×104                  |

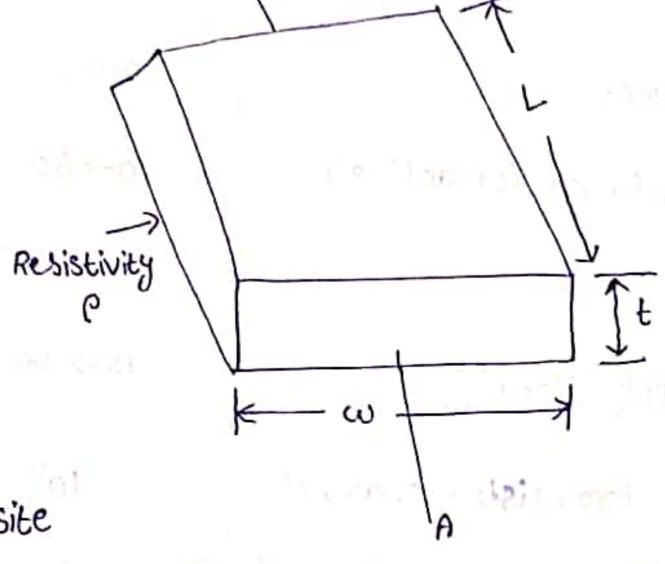

Sheet resistance concept applied to mos transistors and Inverters:

consider n-type transistor has a length L=22 and

width w= ax.

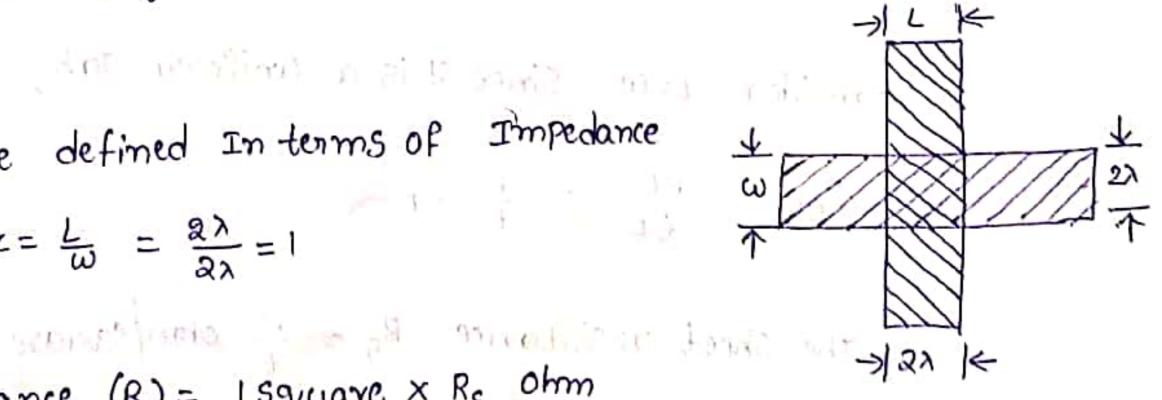

Resistance defined Interms of Impedance 'z' i.e  $z = \frac{L}{\omega} = \frac{2\lambda}{22} = 1$

Resistance (R) = 15quare x Rs ohm Square est rejuste of the follow or never the of enter physical enters

For 54m technology R=10420 Yardania oli li linistikoar sucasa For orbit aum technology R= 2x101 N

$$z=\frac{L}{\omega}=\frac{8\lambda}{8\lambda}=4$$

channel resistance, R=z.Rs

R=4×104 is (for 54m technology)

R= 8x104 N (For orbit aum technology)

#### caluclation of Resistance of a simple Inverter:

For depletion mode, Pull-up transistor

L:w is 4:1

$$R_{p,q} = Z \times R_S$$

$$= 40 \times 10^4 = 40 \times 10^{-10}$$

es designal in an ambacina see 4

Pull-down transistor, L: wis 1:1

Total resistance R= Rp.u+ Rp.d

= 40 Km + 10 Km

Jak H lo nad

the good to paying any about old section.

consider simple cmos Inverter as shown in fig. below

n-type enhance ment mode. - Thirthart Thirthard I in gallo chias - 35 milestants

Area capacitances of Layers:-

For any layer, knowing the dielectric thickness, we can caluclate the orea capacitance

$$c = \frac{\varepsilon_0 \varepsilon_{ins} A}{D}$$

where, A > Area of plates

E > permitivity of free space D > thickness of sion (8.85 x 10 14 F/cm)

rollisment made inst

Eins -> Relative permitivity of Sion = 4

|                          | Value in PFX 104/4m (Relative values in brackets) |             |             |  |

|--------------------------|---------------------------------------------------|-------------|-------------|--|

| capacitance              | 5 km                                              | Rum         | 1.24m       |  |

| Gate to channel          | 4 (1.0)                                           | 8 (1.0)     | 16 (1.0)    |  |

| Diffusion (active)       | (0.25)                                            | 1.75 (0.22) | 3.75 (0.23) |  |

| Polysilicon to substrate | 0.4 (0.17                                         | 0.6 (0.075) | 0.6 (0.038) |  |

| metal 1 to substrate     | 0.3 (0.075)                                       | 0.33 (0.04) | 0.33 (0.02) |  |

| metal 2 to substrate     | 0.2 (0.05)                                        | 0.17 (0.02) | 0.17 (0.01) |  |

| metal 2 to metal 1       | 0.4 (0.1)                                         | 0.5 (0.06)  | 0.5 (0.03)  |  |

| metal 2 to polysilicon   | 0.3 (0.075)                                       | 0.3 (0.038) | 0.3 (0.018) |  |

Note:- Relative value = Specified value / gate to channel Value for that technology

Standard unit of capacitance 15 :-

The unit is denoted by  $\square c_g$ .

It is defined as gate to channel capacitance of a mos transistor having  $\omega = L =$  feature size that is standard.

For any mos process cg is evaluated is For 54m mos circuits:

Area/standard square = 5 4mx 5 4m -> 22 K

= 25 4m

capacitance value from table = 4×104 PF/4m² (:: Grate to channel)

standard value II cg = 254m² × 4×104 PF/14m²

= 0.01 PF

#### ii) For 24m mos circuits:-

Area/standard Succase =  $2\mu m \times 2\mu m = 4\mu m^{\nu}$ Gate capacitance value =  $9\times 10^{4}$  PF/ $4m^{\nu}$ Standard value  $\Box^{c}g = 4\mu m^{\nu} \times 9\times 10^{4}$  PF/ $4m^{\nu}$  = 0.032 PF

#### iii) For 1.2 4m mos circuits :-

Area/standard square =  $1.2 \text{ Am} \times 1.2 \text{ Am} = 1.44 \text{ Am}^{2}$ Gate capacitance value =  $16 \times 10^{4} \text{ PF}/4 \text{ m}^{2}$ .

Standard value  $\square c_{g} = 1.44 \text{ Am}^{2} \times 16 \times 10^{4} \text{ PF}/4 \text{ m}^{2}$ = 0.0023 PF

Thomas of Tree

Some area capacitance caluclations:

consider the area of capacitance

at the contract of the state of

phone of the fell of

Total area =  $20\lambda \times 3\lambda = 60\lambda^2$

min-channel area = 2xx2x = 4x2

(feature Size)

Relative area =

$$\frac{\text{Total area}}{\text{feature size}} = \frac{60\lambda^{2}}{4\lambda^{2}} = 15$$

1. consider the area in metal 1.

capacitance to substrate = Relative area x Relative c value

I WELL

The first file of the property of the second states of the second second

a. consider the same area in polysilicon

capacitance to substrate = Relative areax Relative c value

3. consider the same area in n-type diffusion

capacitance to substrate = Relative area x Relative c Value

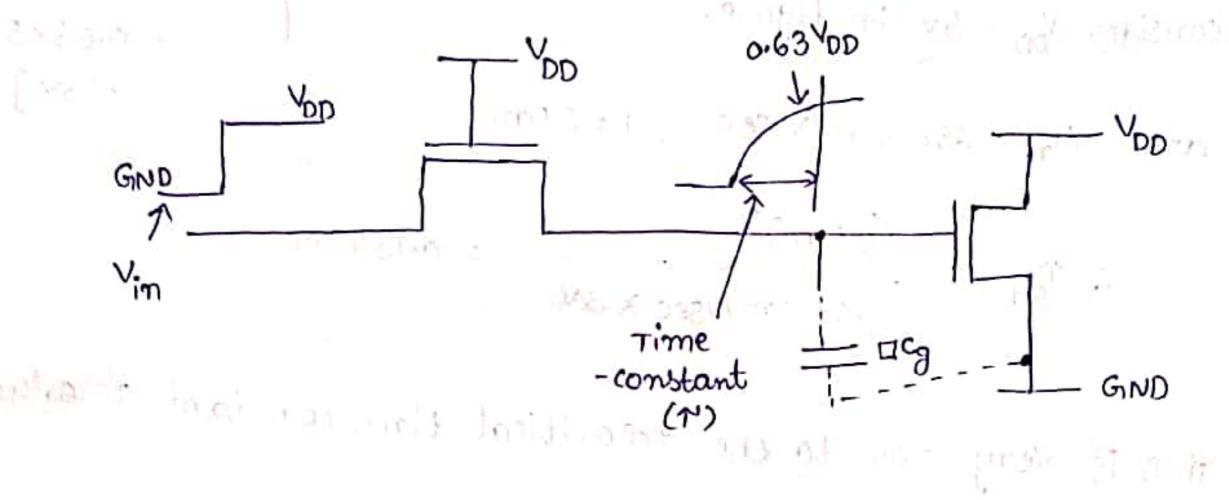

consider the capacitance caluclation in multilayer

and standard gate capacitance unit  $\square cg$ . If we consider the case of one standard (feature size square) gate area capacitance being charged through one feature size square of n-charmel resistance (that is, through Rs for an mos pass transistor charmel) as shown in fig.

Time constant (r) = (IRs (n-channel) ×10 cg) seconds

54m technology

$P = 10^4 \text{ N} \times 0.01 \text{ PF} = 0.1 \text{ msec}$

orbit 24m technology

~= 2x104 N x 0.0032 PF = 0.064 msec

orbit 1.24m technology

N= 12x104 N x 0.00 23 PF = 0.046 nsec

To consider circuit wiring and parasitic capacitances must be allowed for so that the figure taken for N is often Increased

by a factor of 2 to 3 so that for 5 km circuit the worst case delay will be around T = 0.2 to 0.3 nsec.

p is not much different from x Transit time 15d.

$$\frac{\gamma_{Sd}}{Sd} = \frac{L^{2}}{\mu_{m} \gamma_{dS}}$$

Ys varies as of changes from a volles to 63% of 400 in period N.

consider

$$V_{DD} = 5V$$

in figure.

$$\begin{array}{ll}

\text{and} & V_{DD} = 5V \text{ in figure.} \\

\text{and} & V_{DD} = 650 \text{ cm}^2 | V_{DD} - 800 \text{ cm}^2 | V_{DD} \\

\text{and} & V_{DD} = 650 \text{ cm}^2 | V_{DD} - 800 \text{ cm}^2 | V_{DD} - 800 \text{ cm}^2 | V_{DD} \\

\text{and} & V_{DD} = 650 \text{ cm}^2 | V_{DD} - 800 \text{ cm}^2 |$$

This is very close to the theoritical time constant n caluclated above.

Thus the transit time and time constant are synchronous and can be Interchangeably used. The Stray capacitances are usually allowed for doubling the theoritical values caluclated.

For 54m mos technology, N=0.3 insec

For orbit 24m mos technology, N=0.2 nsec

For orbit 1.24m mos technology, N=0.1 nsec

AND AND SOLD TO LOCATE THE CARREST OF THE PARTY OF THE PA

the manual ration in the land and and and and the

consider the basic 4:1 nmos Inverter. In order to achieve 4:1 zp.4 to zp.d ratio, Rp.4 will be 4 Rp.d and if Rp.d is contributed by the minimum size transistor then

so that the delay associated with the Inverter will depend on whether it is being turned on or off.

Fig:- Nmos Inverter pair delay

consider a Pair of cascaded Inverters, then the delay over the pair will be constant irrespective of the sense of the logic level transition of the Input to the first. This is shown in the fig. below and assuming  $\nu=0.3$  nsec and making no extra allowances for wiring capacitance, overall delay  $\nu+4\nu=5\nu$ .

be a notice of all the sent that a sent was a sent when I was

THE PROPERTY OF

Generally, the delay through a Pair of similar Nmos Inverter

is

$$T_{d} = \left(1 + \frac{z_{P,U}}{z_{P,d}}\right) \gamma$$

$$= \left(1 + \frac{u}{1}\right) \gamma = 5 \gamma$$

$$= 2 \gamma \sqrt{5 \gamma}$$

$$|askn R_{P,U}|$$

$$|askn R_{P,U}|$$

$$|askn R_{P,U}|$$

$$|askn R_{P,U}|$$

$$|askn R_{P,U}|$$

$$|askn R_{P,U}|$$

Figu:- minimum size cmos Inverter pair delay

when considering cmos Inverters, the Nmos ratio rule no longer applies, but we must allow for the natural resistance asymmetry in Rs between Pull-up and Pull-down devices usually equal size.

fig (2) shows the theoritical delay associated with a Pair of minimum size Lambda based Inverters. Note that the capacitance (=20cg) is double that of the Nmos Inverter Since the Input to a cmos Inverter is connected to both transistor gates. Note the allowances made for different channel resistances.

The Asymmetry of resistance values can be eliminated by Increasing the width of P-device channel by a factor 2 to 3.

Note that gate Input capacitance of P-device transistor Increased by same factor.

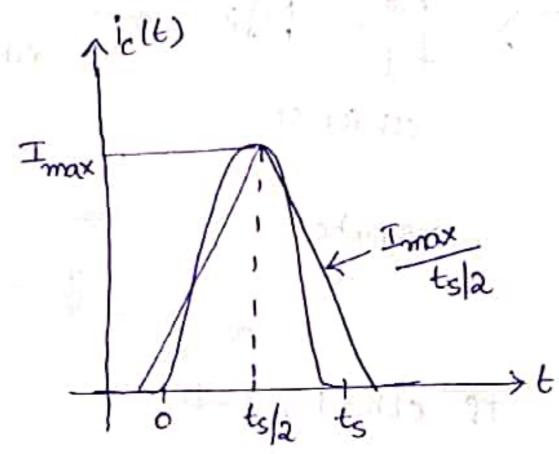

cros Inverter delay estimated by splitting the output transitions into rise time the and fall time the corresponding to changing and dischanging of the capacitive load cu.

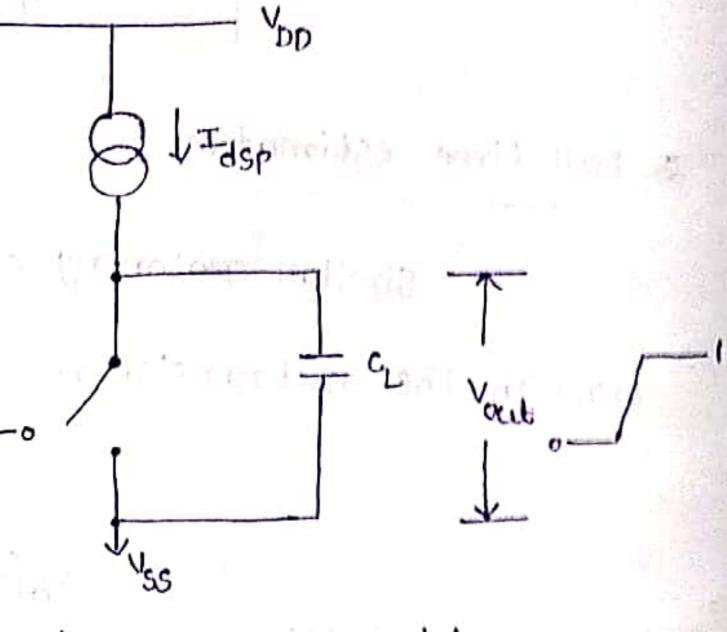

#### i) Rise time estimation :-

assume that P-device stays in saturation for the entire charging period of the load apacitor of.

The current may be modeled as shown in fig. below

saturation current for p-type transistor is given by

This current charges of and magnitude approximately constant,

Vout =

$$\frac{T_{dsp}t}{c_L}$$

=)  $t = \frac{V_{out}c_L}{T_{dsp}}$  — ②

Fig: - Rise-time model

$$\frac{P_{\gamma}}{P_{p}} = \frac{\frac{2 V_{DD} C_{L}}{P_{p} (V_{DD} - 10.2 V_{DD})^{2}}}{\frac{2 V_{DD} C_{L}}{P_{p} (0.8 V_{DD})^{2}}} = \frac{\frac{2 V_{DD} C_{L}}{P_{p} (0.8 V_{DD})^{2}}}{\frac{2 V_{DD} C_{L}}{P_{p} (0.8 V_{DD})^{2}}}$$

$$\frac{\gamma_{\gamma}}{\beta_{P}} = \frac{3C_{L}}{\beta_{P}} \frac{3C_{DD}}{\gamma_{DD}} - 3$$

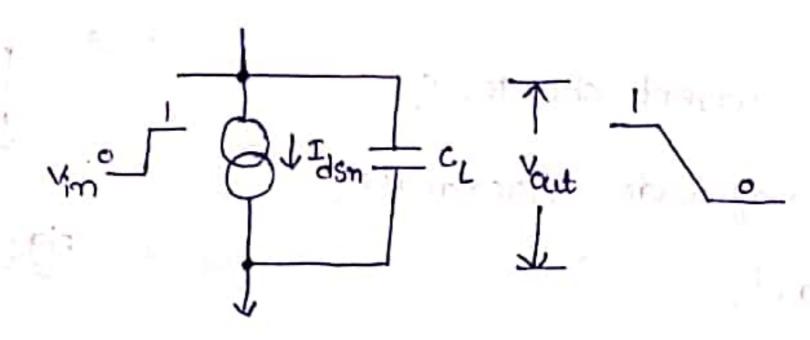

#### 2. Fall-time estimation :-

similar reasoning can be applied to the discharge of CL through the n-transistor. The circuit model as shown in fig. below

to many a state of any and a

Hence, the fall time

$$\frac{\gamma_{f}}{F_{n}} = \frac{3C_{L}}{F_{n} V_{DD}} - 0$$

Fig: Fall-time model

From eq 3, 4) we deduce that

But Mn = 2.5 Mp hence Bn = 2.5 Bp, so that the rise time

is slower by a factor 2.5 when both the n and p-devices are minimum sizes.

To achieve symmetrical operation using minimum channel length we need to keep cp = 2.5 cm and minimum size Lambda based geometries this would result in Invertentaving Input capacitance of IDcg (n-device) + 2.5 Dcg (p-device) = 3.5 Dcg in total.

This is simple model is quite adequate for most Practical situations, but it should be recognized that it gives optimistic results. It provide rise time and fall time as

- 1. Ty and if are proportional to 1/VDD

- 2. Ty and te are proportional to ci

- 3. My = 2.5 Mp for equal n-and p-transistor geometries.

Driving Large capacitive Loads:

The problem of driving comparatively large capacitive loads arises when signals must be propagated from chip to off chip destinations.

Generally off thip capacitances,

CL > 104 11 Cg

The capacitances of this order must be driven through low resistances, otherwise excessively long delays will occur.

For driving large capacitive loads, Invertous should present Low Pull-up and Pull-down resistances

It means that mos devices must be designed with Low L:w ratios to have Low resistance values for Zp.u and Zp.d. These channels must be made very wide to reduce resistance value. which consequence makes the Inverten occupy a larger area.

the minimum feature Size which makes Liw ratio large. Hence gate region area Lxw becomes significantly and large capacitance is presented at the Input. which in turn slows down the rates of change of voltage which takes place at the Input.

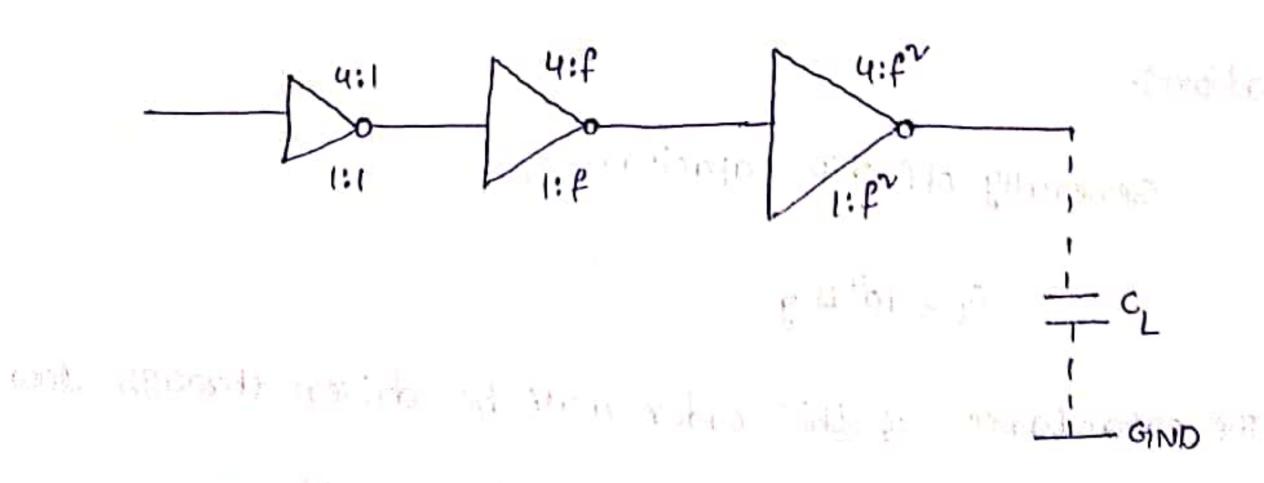

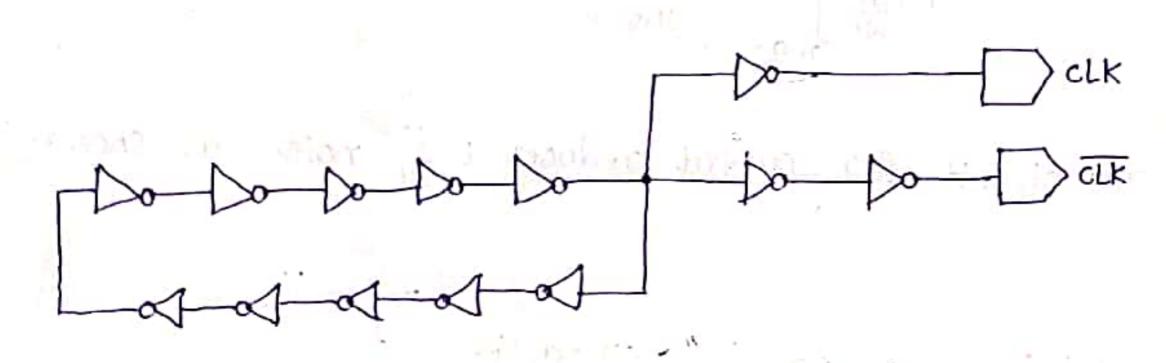

This situation can be Improved by using Neascaded Inverters, each one of which is larger than the preceding stage by a width factor of as shown in fig.

Fig:- Driving large capacitive Loads

The capacitive load presented at the Inverter Input Increases in Proportion to the Increasing width and area also Increases.

Let DVin Indicate a logic o to 1 transition and TVin Indicates Logic 1 to 0 transistion of Input voltage Vin.

Delay per stage = fr for DVin = 4fr for DVin

Total delay per Nmos Pair = 5ft.

similarly delay per cmos Pair = 7ft.

Let  $Y = \frac{C_L}{Dcg} = f^N$

f, N -> Independent values.

Henry English William S. Their ages

Ji 107 9 - 1 16 " " 195'8 28, 1]

Elita man mark hallon

1.00 6

To determine value of if which will minimize the overall delay for given value of y.

ln(Y) = N ln(f)

N= In(y)

N> even

73 Photo

Total delay = Ng stN = 2.5 Nf N (NMOS)

$(0.7) = \frac{N}{2}7fN = 3.5 NfN (cmos)$

In all cases, delay & NFT = Incy) Fr

Total delay is minimized if 'f' assumes the value e.

Assume f=e,

Noiof stages N= In(4)

FOY N EVEN, ty = 2.5 ent (nmos) = 3.5 ent (cmos)

Nodd,

$$t_d = [2.5 (N-1) + 1]e^{\gamma t}$$

(NMOS)  $t_d = [3.5 [N-1) + 2]e^{\gamma t}$  (cMOS)

and

$$t_d = [2.5 (N-1) + 4]e^{\gamma t}$$

(NMOS)  $t_d = [3.5 (N-1) + 4]e^{\gamma t}$  (NMOS)  $t_d = [3.5 (N-1) + 5]e^{\gamma t}$  (CMOS)

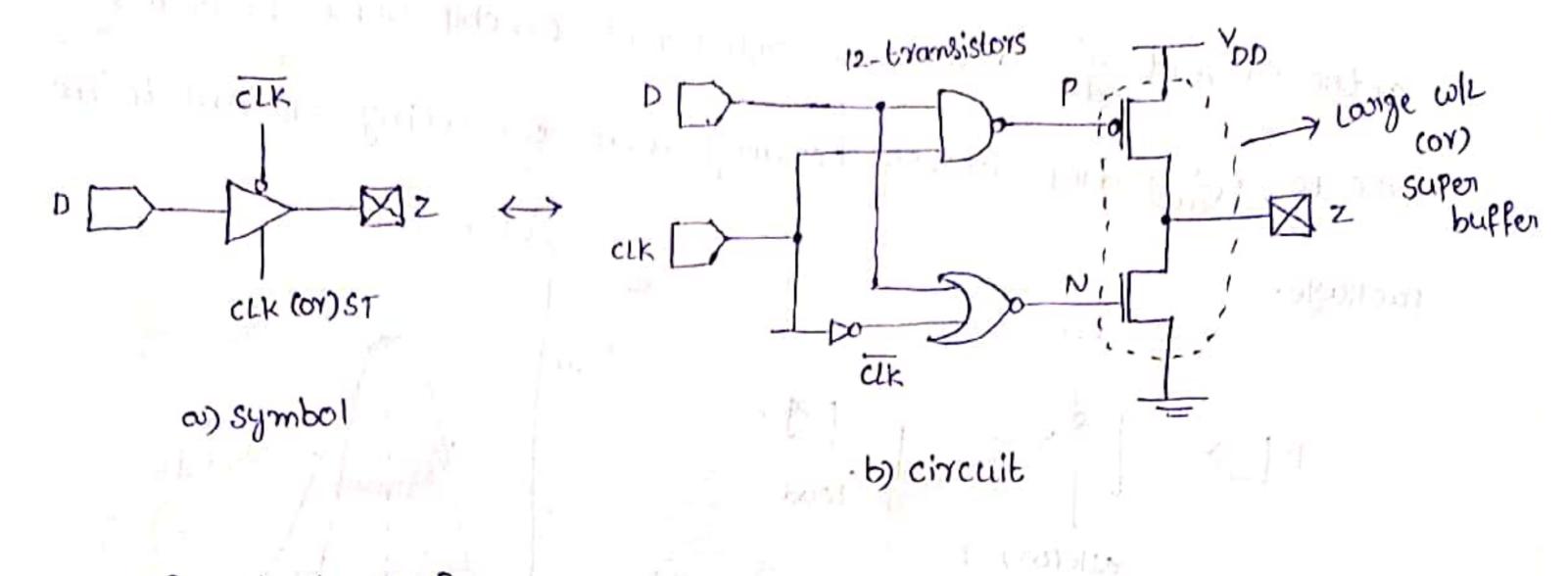

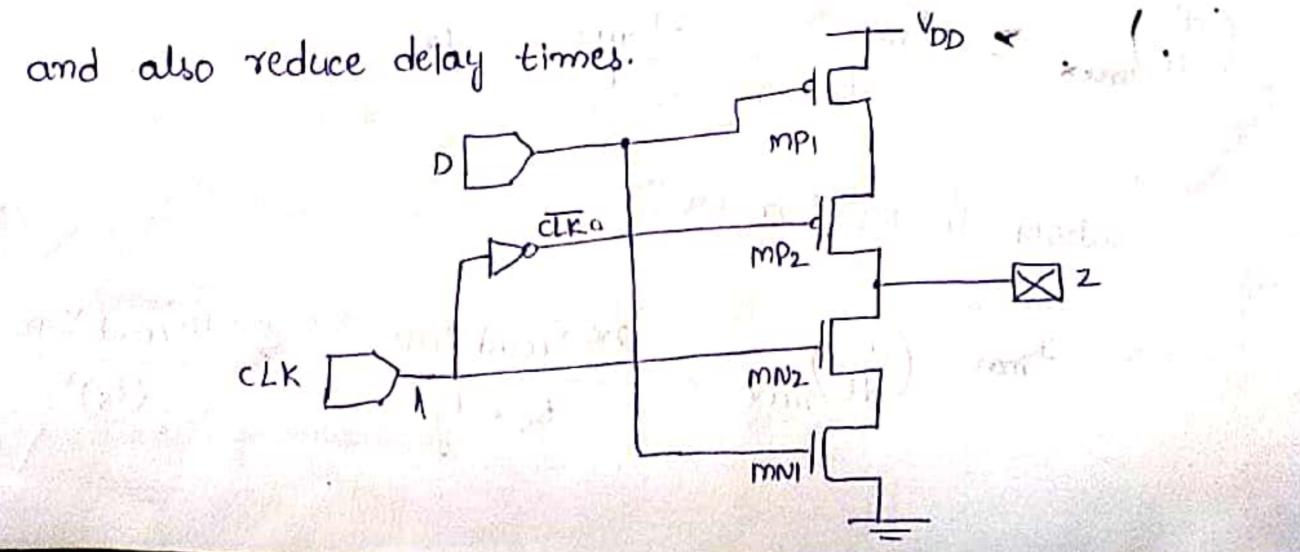

### 2. super buffers:

Theore are 2 types 1. Inverting type nmos super buffer 2. Non-Inverting type Nmos super buffer

# 1. Inverting type Nmos super buffer:

consider a positive going logic transition Vin at the Input, it will be seen that the Inverten formed by T, To is turned on and gate of To is pulled down

toward o' voits with a small delay. Fig:- Inverting type Nmas super buffer Thus To is cut off while To is turned on and octput is allowed pulled down Quickly.

Now consider the opposite transition: when Vin drops to 'o' volt, then gate of T3 is allowed to rise exickly to VD.

Thus Ty also turned off by Vin, T3 is made to conduct with VDD on its gate, in twice the average voltage that would appear if the gate was connected to source in the conventional Nmos Inverter. Now, as Ids x ys, doubling the effective Vgs, Increases the current and reduce the delay in charging at load capacitance of the output, so more symmetrical transitions are achieved.

2. Non-Inverting type Nmos Super buffer:- 0 1

To gain an Idea of the effective ness of super buffers designs, we note that the structures fabricated in 54m technology are capable of driving capacitance of 2pp with rise time of 5msec.

IlP olp

Fig:- Non- Inverting type Nmos Super buffer

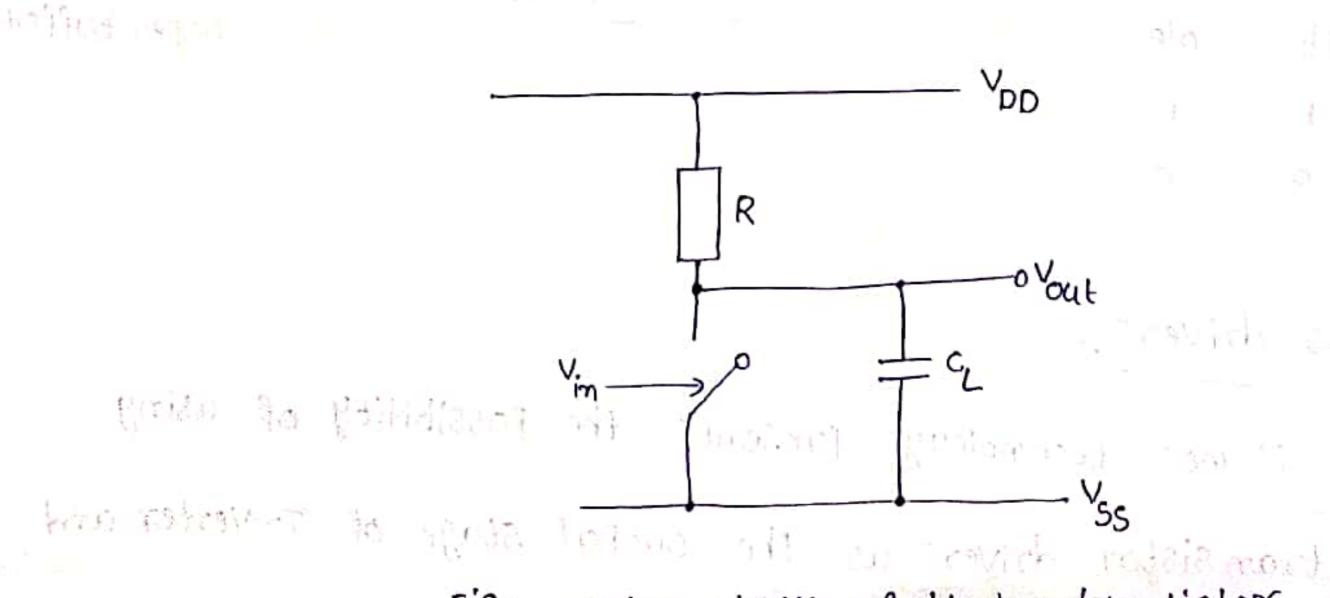

#### 3. Bicmos drivers:-

Bicmos technology presents the Possibility of using bipolar transistor drivers as the output stage of Inverter and logic gate circuits.

In bipolar transistors, there is an exponential dependence of the collector current Ic on base to emitter voltage VBE. Hence the bipolar transistors operated with much smaller Input voltage swings than mos transistors and still switch larger currents. only a small amount of charge must be moved during switching.

Another consideration in bipolar devices is that of the temperature effect on Input voltage Vbe. Vbe dependent on base width wb, doping level NA, electron mibility un and collector-current Ic, it is linearly dependent on temperature. Now the temperature dependences across an Ic are not very high Thus the Vbe values of bipolar devices spread over the chip remain matched and donot differ by more than few millivolts.

The switching performance of a bipolar transistor having a capacitive load can be analyzed with help of equivalent circuit as shown in figure

Fig:- Driving ability of bipolan transistor

The time st revuired to change the output voltage Yout by an amount evual to Input Voltage Vin is

c<sub>L</sub> > Load capacitance

<sub>m</sub> > Transconductance

The value of st is small because transconductance (9m) is higher.

The delay due to bipolar transistor reveals that it has a components Tim and TL

- i) Tin: To charge the base emitter Junction of bipolar transistor.

The time is typically 2ns for Bicmos transistor based driver.

Charge driver require Ins for Tin to charge Input gate capacitance.

In case of GaAs driver is almost 50-100 ps.

- ii) IL:- Time revuired to charge output load capacitance cland equals (VIId) (1/hpe) cl. This is less for bipolar driver by a factor he as compared to mos drivers.

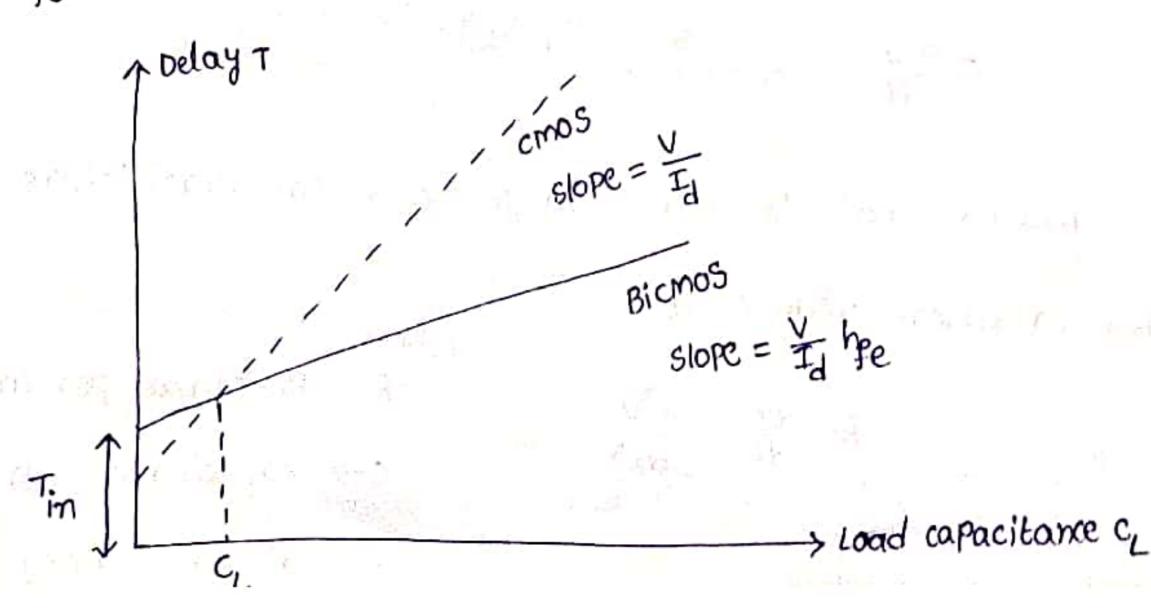

#### propagation delays :-

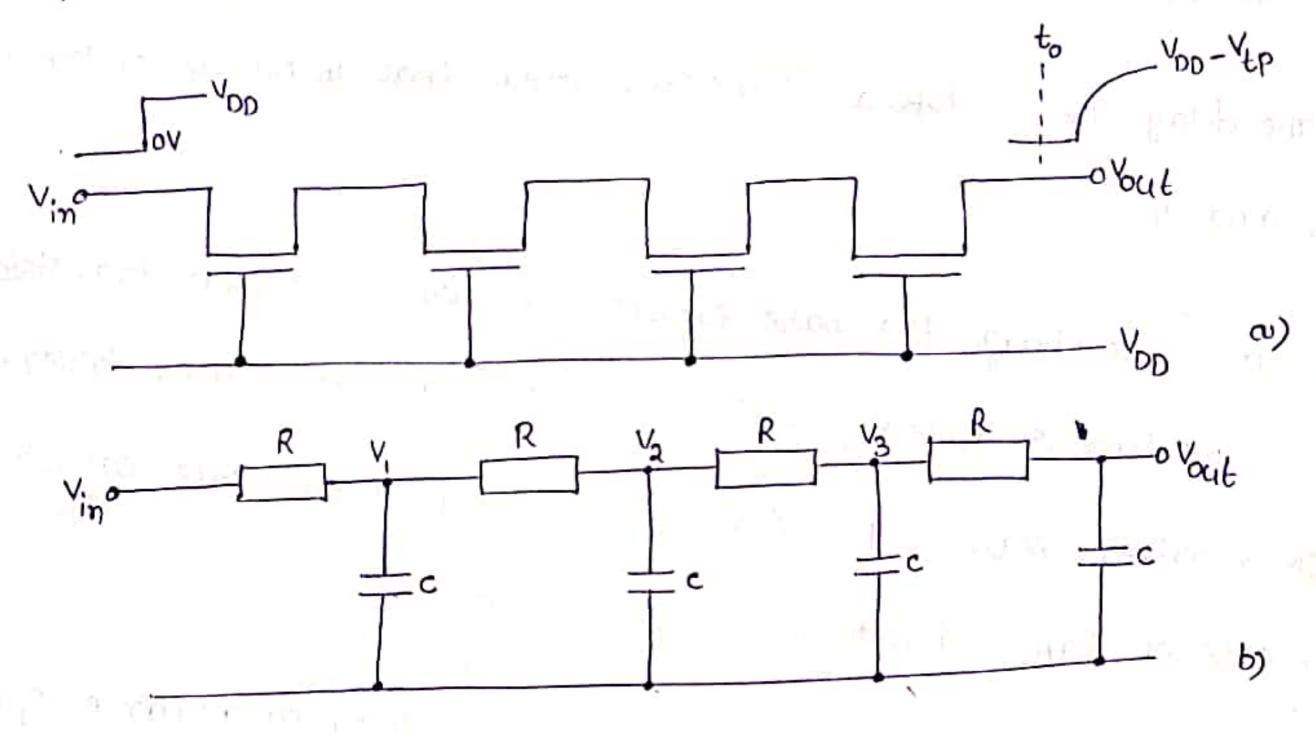

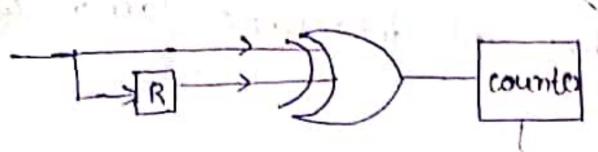

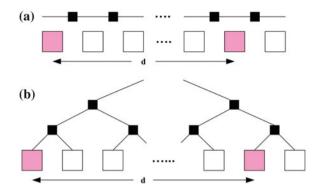

#### 1. cascaded pass transistors :-

The pars transistors used as parallel (or) series combination of switches in logic arrays.

consider a chain of 4 pass transistors connected in series, the gate of each transistor connected to VDD (109ic1).

Fig:- propagation delays in pass transistor chain

Apply KCL at node 1/2,

J. Spedinger Specie

$$c \frac{dV_2}{dt} = I_1 - I_2 = \frac{(V_1 - V_2) - (V_2 - V_3)}{R}$$

Assume that there are large no of pass transistors in series. Then equation reduces to

$$RC \frac{dV}{dt} = \frac{d^2V}{dx^2}$$

where,

R→ Resistance per unit length

c→ capacitance per unit length

x→ distance along the Network

from Input

(12)

The propagation time  $r_p$  for a signal to propagate a distance x is  $r_p \propto x^p$

Let define variables rand c such that R=rRs and c=clicy are lumped Network elements Rand c. Then total network element is

Actually 'r' is relative resistance per section in terms of Rs and c. Total time delay r, for 'n' section is

$$\left[\frac{\gamma}{d} = \gamma^{\gamma} C \gamma (\gamma)\right]$$

If 'n' Increases, total delay Increases and in Practice no more than upass transistors connected in series. If the number can exceeded a buffer is Inserted between each group of 4 Pass transistors.

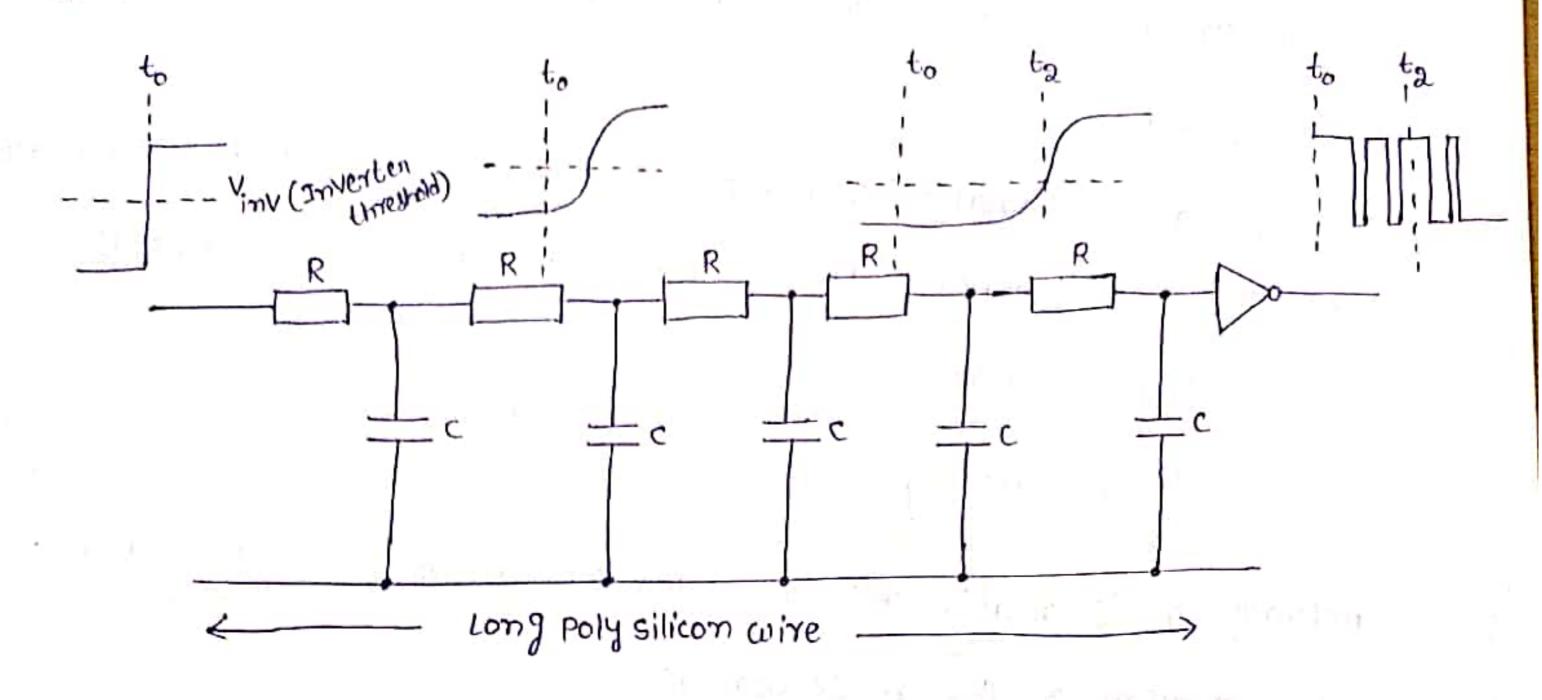

# 2. Design of Long polysilicon wires:

For long polysilicon wires, use buffers mainly

i) signal propagation is speeded up ii) Reduction in sensitivity to noise

Introduction of delays in signal Propagation makes the signal move susceptible to noise as shown in fig. below

In diagram, the slow rise time of a signal at the Input of Inverter means that the Input Voltage spends a long time in the Vicinity of Vinu so that Small disturbances due to noise will

The fact of the first of the state of the st

switch the Inverter state between 'o' and 'I' as shown in output.

Hence it is necessary that long polysilicon wires by suitable buffers to avoid the effects of noise and to speed up the rise time of propagated signal edges.

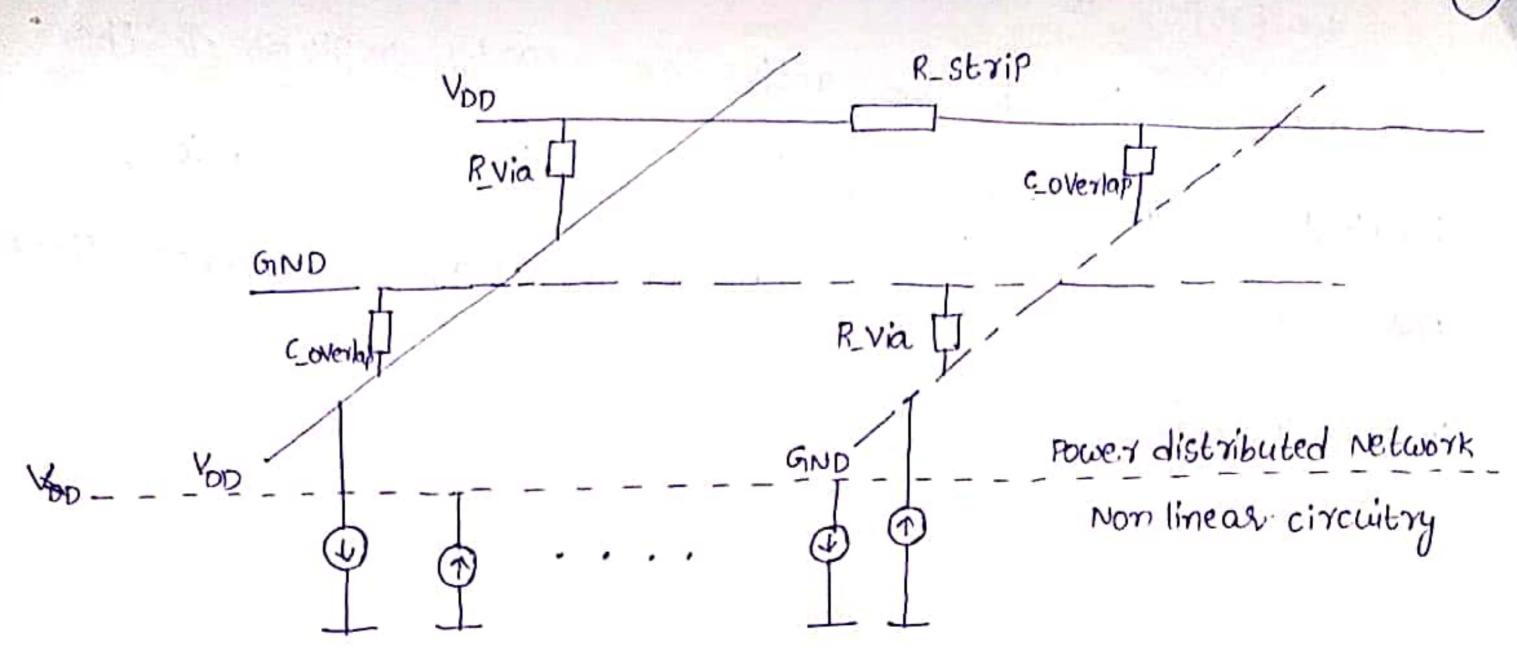

### wiring capacitances:

The Various sources of capacitance that contribute overall wiring capacitance are

- 1. Fringing fields

- a. Inter layer capacitances

- 3. Peripheral capacitances

## 1. Fringing fields:-

It can be major component of the overall capacitance for Interconnect wires.

For fine line metallization, the value of fringing field capacitance (Cff) can be same order as the area capacitance.

Thus cfe should be taken into account if accurate prediction is needed

$$c_{ff} = \xi_{io_2} \varepsilon_{ol} \left[ \frac{\pi}{2n \xi_{1} + 2d (1 + \sqrt{1 + \frac{1}{d}})^2} - \frac{t}{4d} \right]$$

where l-> length

to thickness of cuire

d > wire to substrate separation

Total capacitance,

$$c_w = c_{area} + c_{ff}$$

#### White of the mat thinger is on the said 2. Inter layer capacitance:-

There is a chance to exists a capacitance between the layers due to parallel plate effects. 10-10 coli 3

This capacitance will depends on the Layout, whether the layers cross (or) when one layer underlies another

For regular structures it is readily calliclated and contributes significantly to the accuracy of circuit modeling and delay caluclations. nicing conditional algorith throat proversh again

# 3. peripheral capacitance:-

The source and drain n-diffusion regions forms Junctions with the p-substrate (or) p-well at well defined and uniform abstract and event assistant demand depths.

Similarly for P-diffusion regions in forms Junctions with the n-substrate (or) n-well at well defined and uniform depth s.

For diffusion regions each diode thus formed has associated with it a Peripheral capacitance of diffusion region to substrate; smaller the source (or) drain area greater the relative value of peripheral capacitance.

Total diffusion capacitance is given by

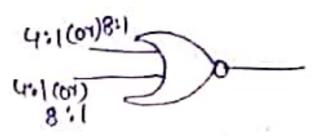

Fan-IN and FAN-OUT:

FAN-IN: - The no. of Inputs to a gate is called FAN-IN

FAN-OUT: - The no. of gates and length of metal tracks connected to its output

Choice of Layers:

The following rules must be considered for the proper choice of layers

- is except for very small distances, polysilicon should not be used for routing you and yss.

- ii) long lengths should be used only after careful considerations because Polysilicon layer has relatively high value of Rg.

- iii) VDD and Vgs (GND) must be distributed only on metal layers. This is also due to Rs Value

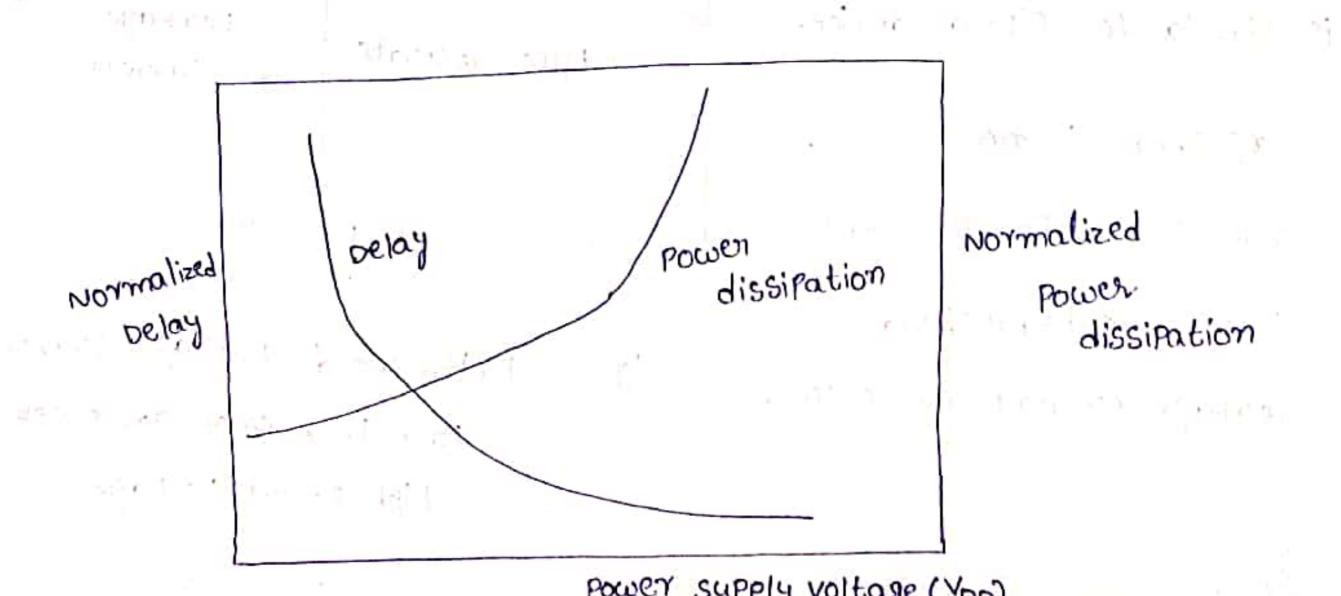

### scaling of mos circuits

scaling models and scaling factors:

scaling means reduce the dimensions (size) of the mos transistors.

There are 3 Scaling models

- 1. constant field scaling

- 2. constant Voltage saling

- 3. Lateral Scaling ...

Fig:- scaled nmos transistor

#### 1. constant field Scaling: - 22 and the state of the

All the parameters in mosfET are scaled by the factor & except supply voltage you and gate oxide thickness tox.

## 2. constant Voltage scaling:

The supply voltage boo and gate oxide thickness tox are 1 - 100 de 0 scaled down by B.

# 3. Lateral scaling:-

This is combined model of constant field and constant voltage scaling.

# scaling factors for device parameters:

1. Grate area (Ag):

L> channel width

the character of heart, some south

police of willy dreder to the

Ag is scaled by 1/2

2. Gate capacitance per unit area Co (or) Cox:

$$c_0 = \frac{\varepsilon_{ox}}{D}$$

where  $\epsilon_{ox} \rightarrow Permitivity of gate oxide to$

D -> gate oxide thickness

$$c_0$$

is scaled by  $\frac{1}{VB} = B$

3. Gate capacitance (cg):-

G > B, WL > L

$$c_g = \frac{\beta}{\alpha^{\gamma}}$$

cg is scaled by B

torisional water je scaling.

A Cortions of a thirt includes

of pd such helos

forther harting

Ax > Area of depletion region d > depletion width

Ax is scaled by 1/22 d is Scaled by 'k'

$$c_{\chi} = \frac{1}{\alpha^{\gamma}}/\frac{1}{\alpha} = \frac{\kappa}{\alpha^{\gamma}} = \frac{1}{\alpha}$$

5. carrier density in channel (Quon):-

Ovon is average change per unit area in the channel in ON State.

of policed by P

co scaled by B Ygs scaled by 1/B

iscaling factor (Non) = Big =1 enations factor (Jase) = P(+)

channel resistance (Ron):-

4-4 covier mobility in channel

$$f_0 = \frac{\omega}{L} \cdot \frac{4 c_0 v_{0D}}{c_g}$$

$$J = \frac{I_{dss}}{A}$$

A -> cross sectional area which is scaled by 1/2"

di di balan ai

: Scaling factor (J) =

$$\frac{1/\beta}{1/\alpha^{\gamma}}$$

=  $\frac{\alpha^{\gamma}}{\beta}$

## 10 Power dissipation per gate (Pg):

power dissipation per gate consists of atypes in Static and dynamic.

static power dissipation takes place when device holds a particular state Dynamic power dissipation takes place when device changes its state.

Pg (dynamic) scaled by

$$\frac{1}{\sqrt{p}} \cdot \frac{\sqrt{r}}{p} = \frac{1}{p^{r}}$$

rof somboni prilar.

- T all brokenson

en hand eight midden in of halver entre ditional halberton it flore 1. switching energy per gate ( ):-

$$E_g = (V_{00})^{\gamma} \cdot \frac{c_g}{2}$$

Power dissipation per unit area (&):-13.

$$a = \frac{p_9}{p_9}$$

V. B. B. V. J. b.

: saling factor for

$$R_0 = \frac{(-\frac{1}{12})}{(-\frac{1}{2})}$$

14. speed Power Product (Pr):-

: scaling factors for PT = pr. Br.

Breezewich enabled the Jest and

The transfer (Sincore (La))

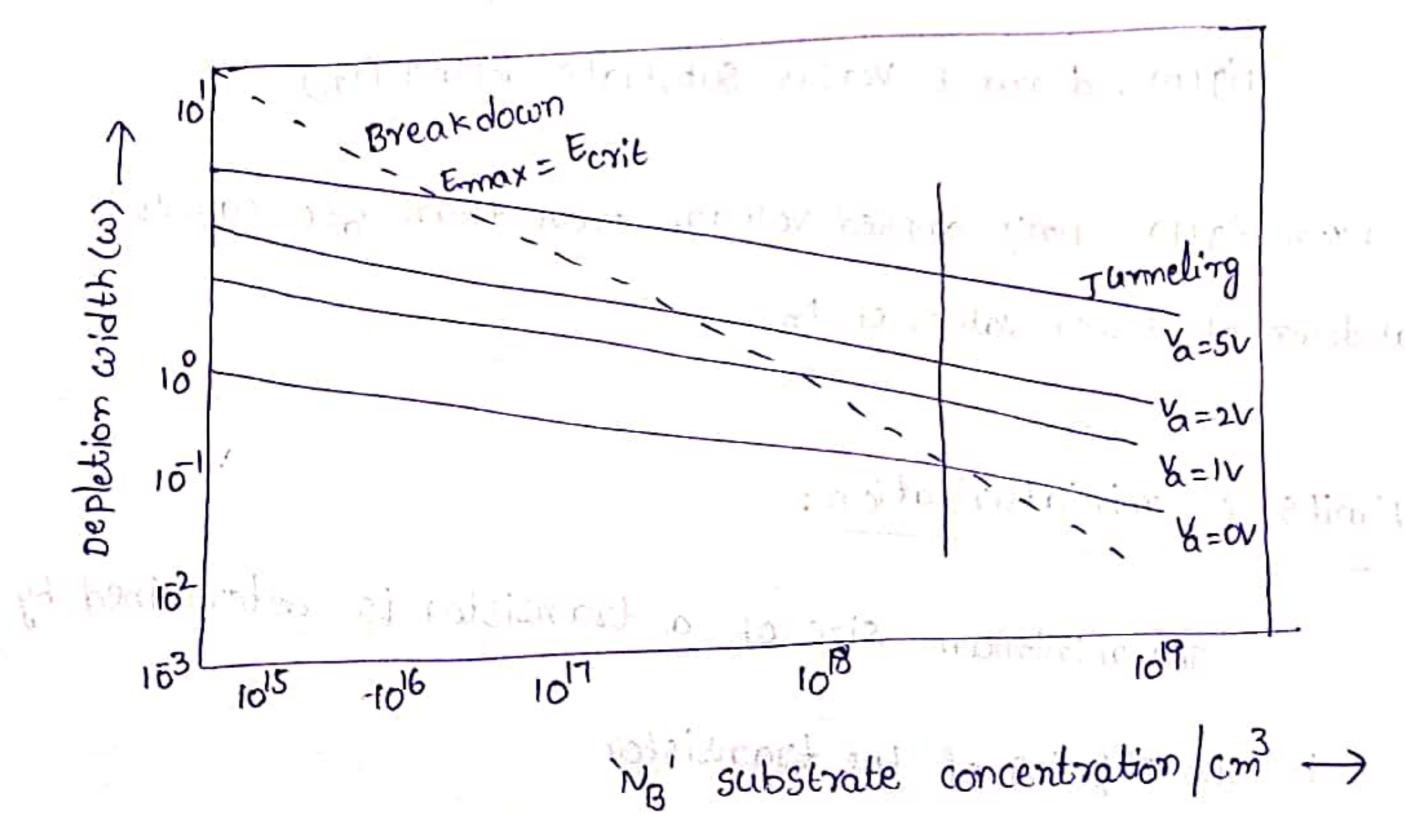

Limitations of scaling:-

is substrate doping:-

Substrate doping level has a direct relation with the built in Potential Counction potential) VB. consider VB is Small as compared with VDD.

Scaling factors for substrate doping:

scaling Involves reduce the charmel length of nos transiste. The depletion region widths must also be scaled down to prevent the source and drain depletion regions from meeting.

Depletion region width d'is

where

Esi > Relative Permitivity of silicon = 12

Es > Permitivity of free space = 8.85 x1014 F/cm

V> Effective Voltage = Va+VB

4 > Applied voltage (maximum value = VDD)

VB > Built-in Potential (Junction Potential)

a > change of electron

My - doping level of substrate

and

$$V_B = \frac{kT}{v} ln \left( \frac{N_B N_D}{n_i v} \right) - 2$$

ND -> donar concentration of source/drain n; -> Intrinsic covier concentration

For the combined voltage and dimension saling model applied riniand of 19000 per to transistor, m-> Real number,

scaling factor for elepholica colding

31 - E = xo. d  $V = \frac{1}{4} + \frac{1}{8}$   $V = \frac{1}{8} + \frac{1}{8}$

If the applied voltage Va is scaled by 1/13 we have

$$= \frac{m V_B + \beta V_B}{\beta} = \frac{(m+\beta) V_B}{\beta}$$

From ears,

$$V_B = \frac{V}{m+1}$$

— 6

substitute ev6 in 3

=)

$$\frac{1}{s} = \frac{m+\beta}{\beta(m+1)}$$

$\rightarrow$  scaling factor

Vs is the effective scaled voltage across depletion region.

No should scaled by  $\frac{\alpha^{\nu}(\beta+m)}{m+1}$  so that scaling factor for d is mider in the seal to see the

1/2.

scaling factor for depletion width:-

from ev. O, as NB Increased to reduce the depletion width and Increases the threshold voltage 4.

maximum electric field Induced in the Junction is

If NB is Increased by a factor & and if \20, then VB Increased by Ina and dis decreased by Ina

Therefore, the electric field E' across the depletion region is Increased by Ja/end and will reach critical level Forit with Increasing Ng.

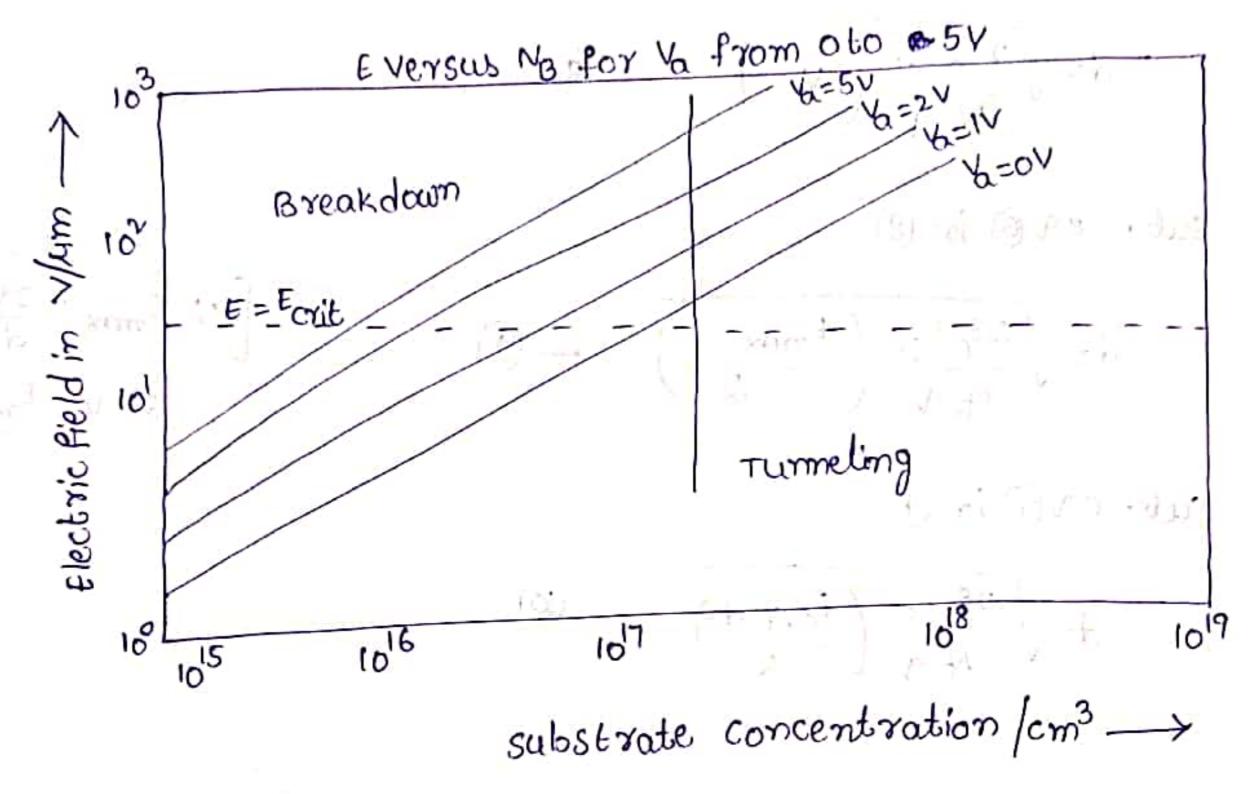

The maximum fig (a) shows the depletion width it as a function of substrate concentration NB and supply voltage VDD. The dashed lines Indicates the max. depletion width for Emax = Ecrit. adaptil servente e pl se andresse e Fromer

$$d = \int \frac{2 \varepsilon_0 \varepsilon_{si}}{N_B q} (v) - 8$$

sub. ear 6 in 8

$$\begin{cases}

:: E_{max} = \frac{2V}{d} \\

=) V = E_{max} d$$

sub ear in @

substrate concentration

In Fig (w), the region above dashed line is that whom the Increased electric field 'E' will induce breakdown.

The maximum electric field Emax in depletion layer as a function of No as shown in fig (b).

Fig (b): d and E Versus substrate doping (NB)

From fig.(b), Any applied voltage more than 1/20 causes breakdown at lower values of NB.

# ii) Limits of miniaturization:-

The minimum size of a transistor is determined by

- in the physics of the transistor

- ii) The technology Involved in fabrication process.

The reduction of device geometry currently dependson alignment accuracy and resolution of Photolithographic technology the limit on feature size is at 0.3 4m which may be reduce the Size using E-beam technology.

The size of transistor is defined in terms of channel length The time for an electron to travel from source to drain 1. depends on channel length L.

Bryo T world Housest 1 (U) F (i) The maximum carrier drift velocity is approximately equal to Librates of Uniter Cornect and Contact Desire Sab.

The minimum transit time corresponds to minimum size formula been a smaller dalate will transistor for Va=oV.

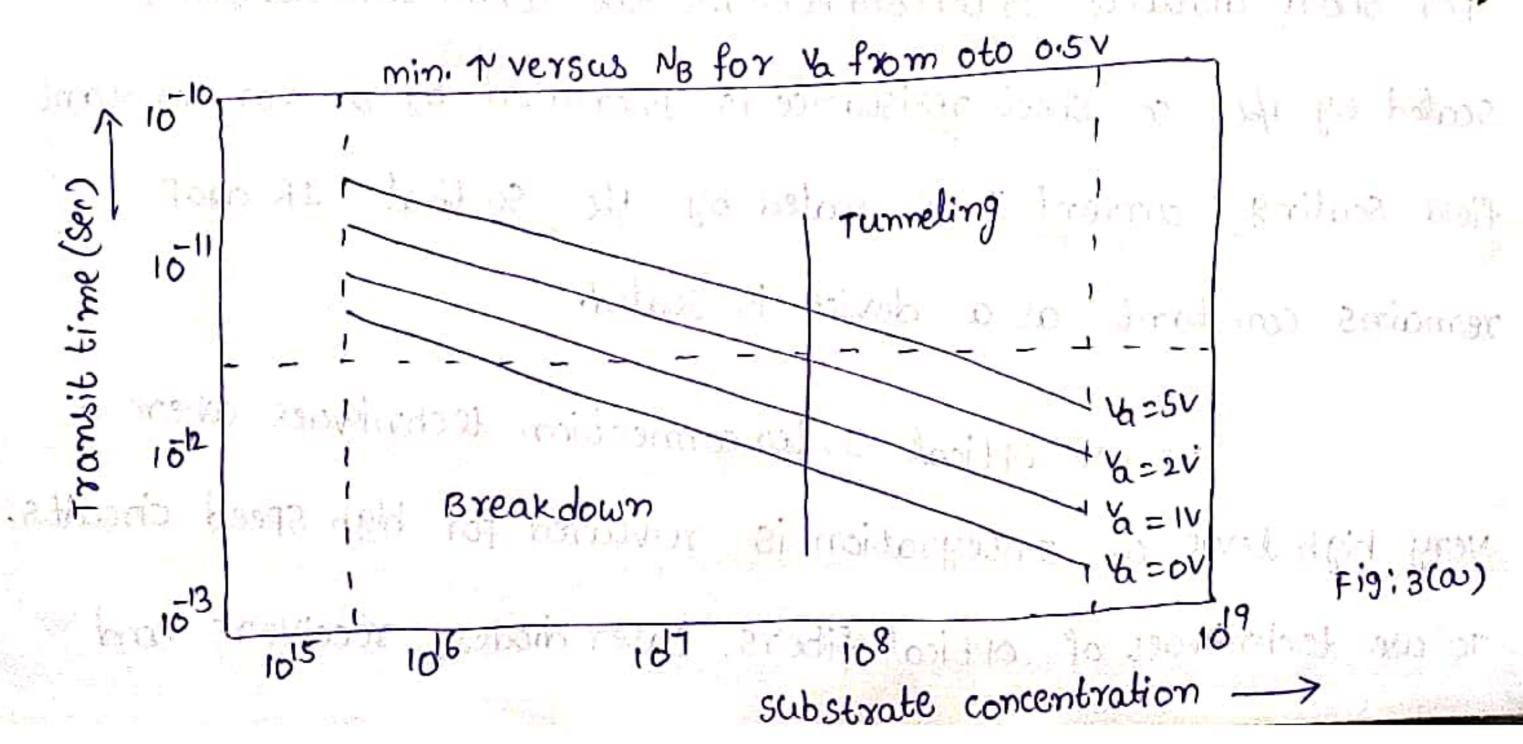

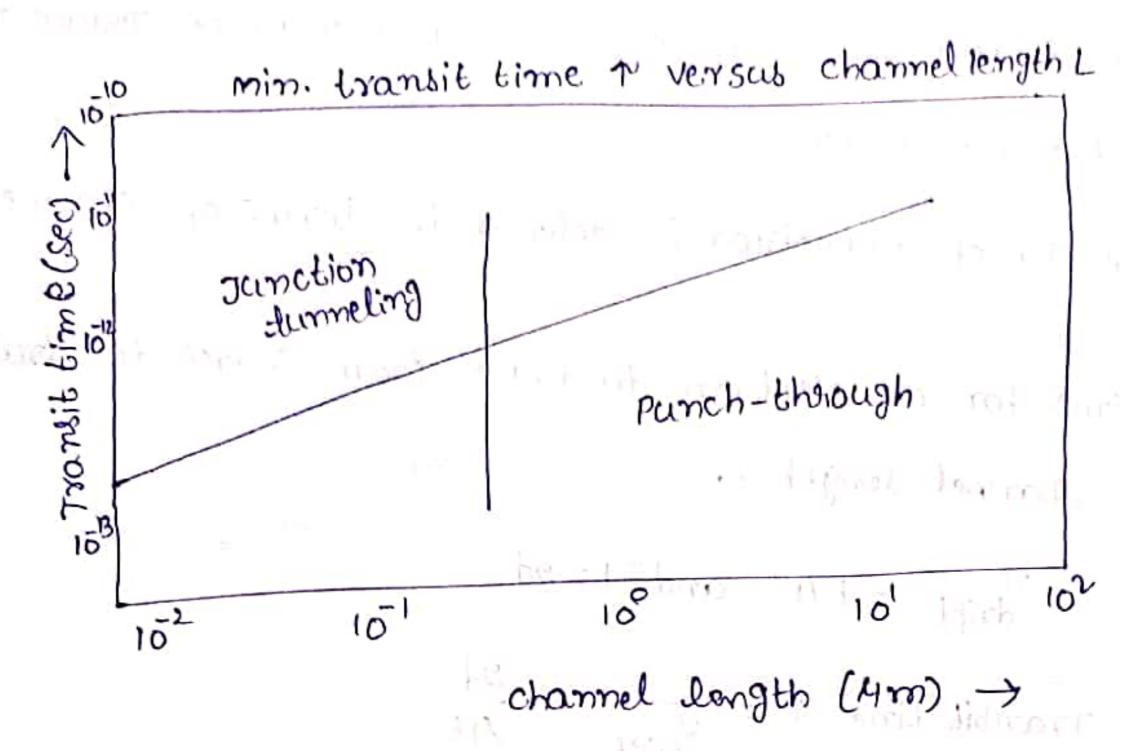

Transit time as a function of NB and L is shown in fig 3(a), (b)

Fig 3(a) assumes transistor size L=2d with zero space between source and drain depletion regions.

Fig 3(b): Transit time 1 versus L.

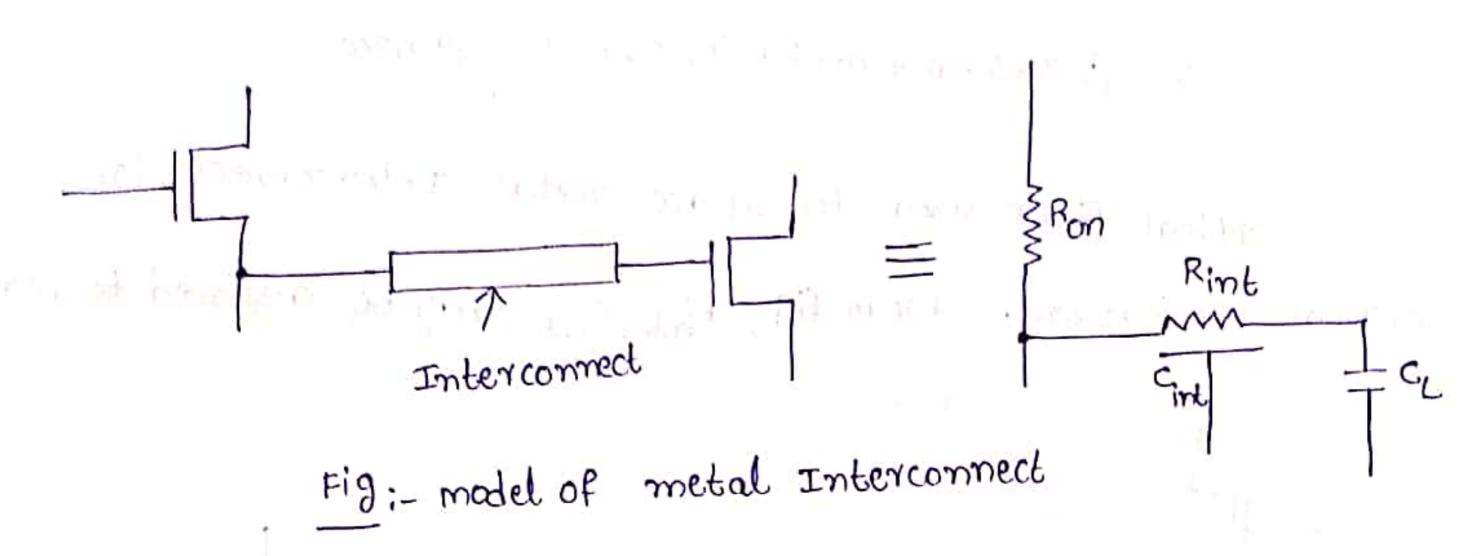

# iii) Limits of Interconnect and contact resistance:

The width, thickness and spacing of Interconnects are scaled by 1/2, cross-section areas must scaled by 1/2.

For short distance Interconnections the conductor length is scaled by 1/2, so sheet resistance is Increased by x. For constant field scaling, current I is scaled by 1/2 so that IR drop remains constant as a device is scaled.

to use optical Interconnection techniques where a very high level of Integration is revuired for high speed circuits. To use techniques of optical fibers, Later diodes, receivers and

Amplifiers must be Included in the Integration circuit. performance will vary with motal materials used. But, rough estimations can be made for with metal Interconnects.

The propagation delay Tp along a single aluminum Interconnect can be calculated from

$$T_{p} = R_{int} c_{int} + 2.3((R_{on} c_{int}) + (R_{on} c_{L}) + (R_{int} c_{L}))$$

where  $T_{p} = 2.3(R_{on} + R_{int})^{C}$  int

where L, ward H are length, width, Height of Interconnect P-> Resitivity of Interconnect

Pon > Transistor on resistance

Rint -> Resistance of Interconnect cint -> capacitance of Interconnect

tox -> Thickness of dielectric oxide

Eox = 3.45 x 105 PF/4m -> Permitivity of sion

consider P=3410-cm for Aluminium, tox = 0.814m for thick oxide L=1cm, w=34m, H=14m then Tp is given by

Tp = (a.3x5kN+ 0.1 KN) 2.5x1012 = 29 nsec

optical fibers used to replace metal Interconnects in critical applications. From fig, Rint, cint may be assumed to zero.

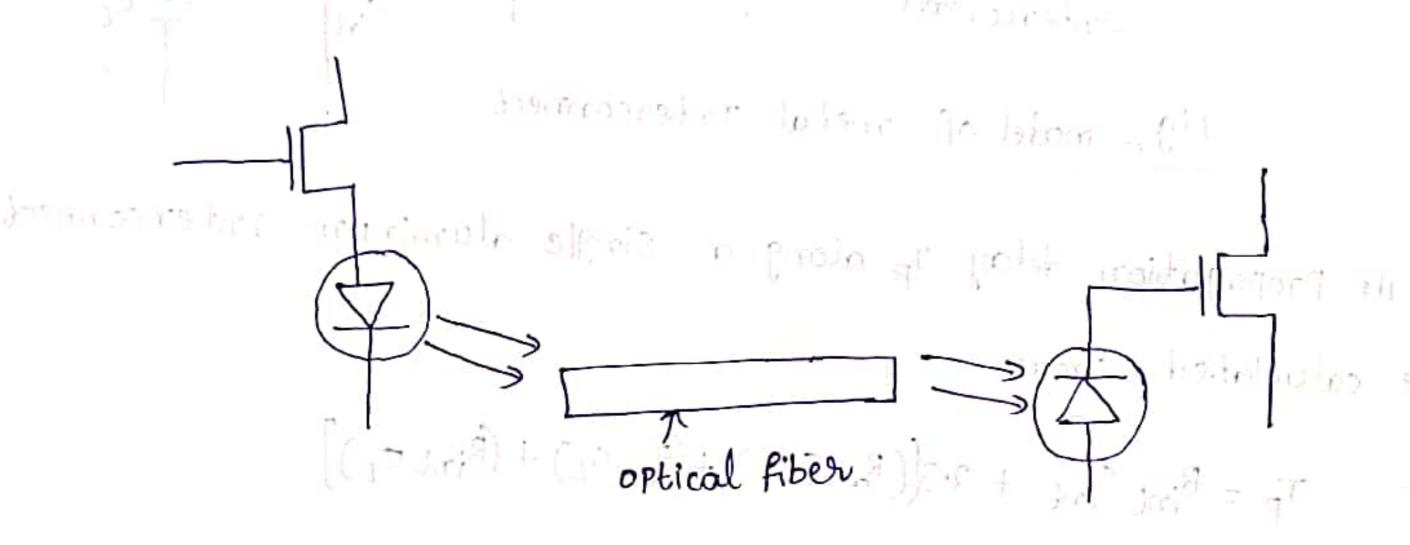

Fig:- Electro-optical Interconnection

Tp = 2.3 Ron CL + tlaser + tint + trec

where, c, > Input capacitance of laser diode

taser > Delay time through laxer diode

tint > propagation delay time along the optical fiber

Interconnect

trec -> Receiver delay time

tint = nL where L-> length of fiber

n > Refractive Index of optical fiber

material

c > Speed of light

Laser diodes and receivers are high speed devices raving self-delays arround 100 psec. The refractive Index is between 1.5 and 2. capacitance of discrete laser dide about IPF. The propagation delay using these values,

$$T_p = 2.3 \times 5 \times 10^3 \times 1 \times 10^{12} + 1 \times 10^{10} + 2 \times 10^{4} + 1 \times 10^{10} = 11.7 \text{ nsec}$$

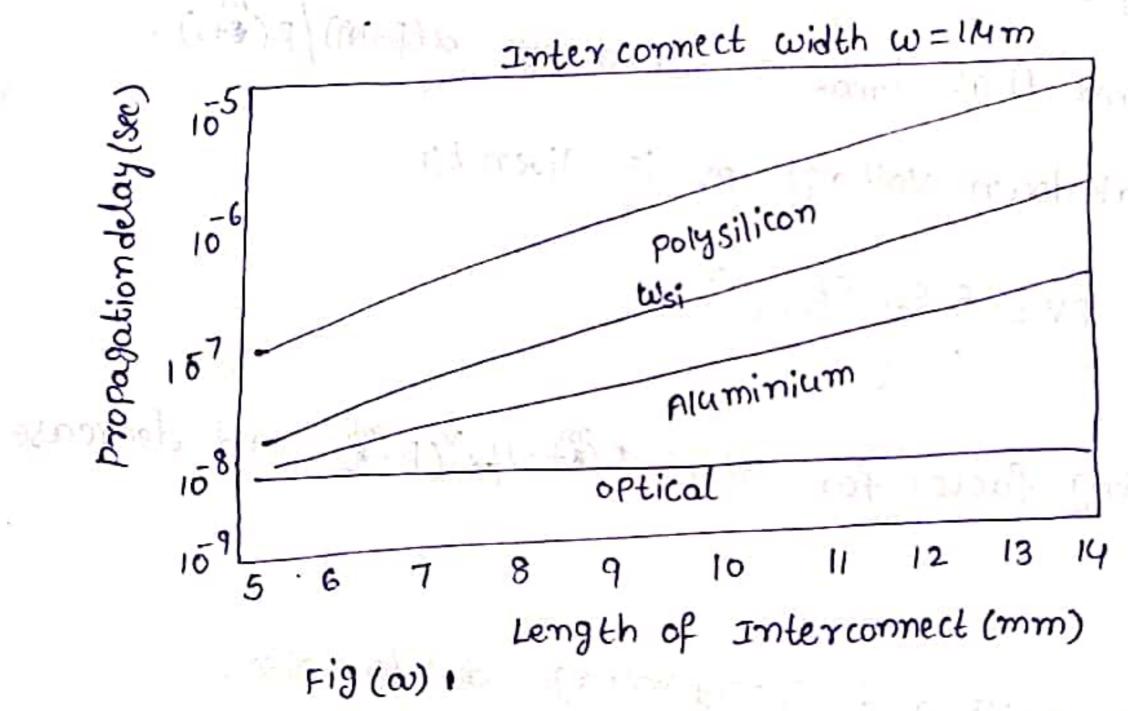

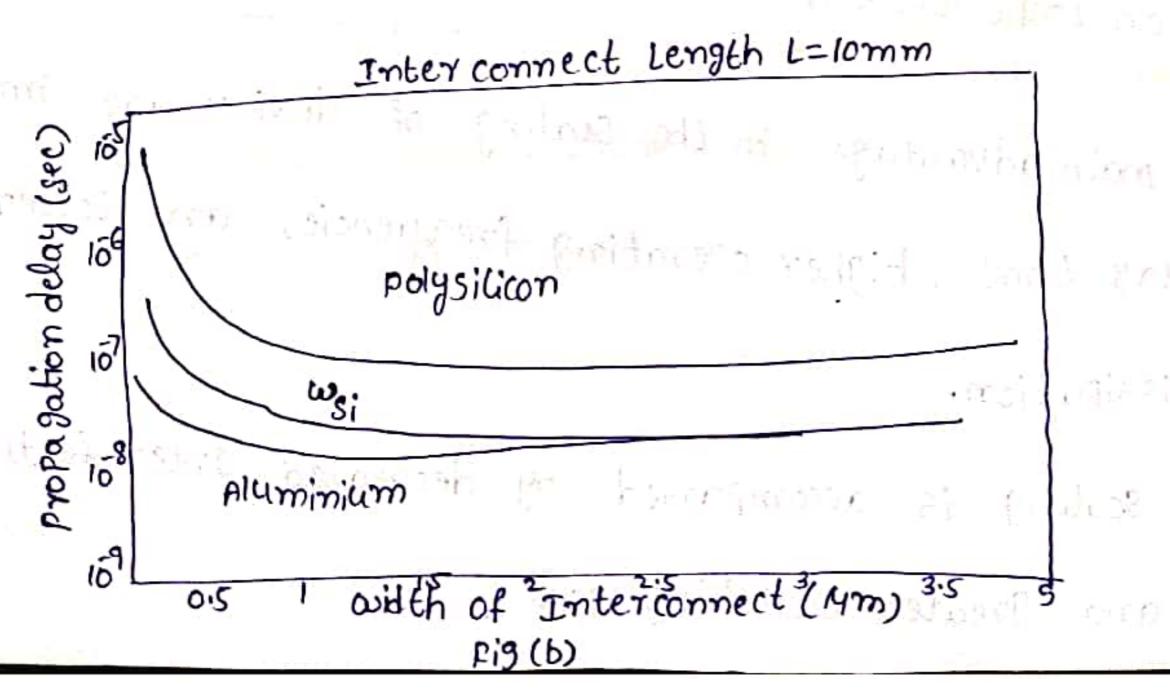

The propagation delay against varying length 'L' of Interconnects are shown in below fig (a) & propagation delay against width of Interconnect as shown in fig (b) 13 Podlov rush Amond

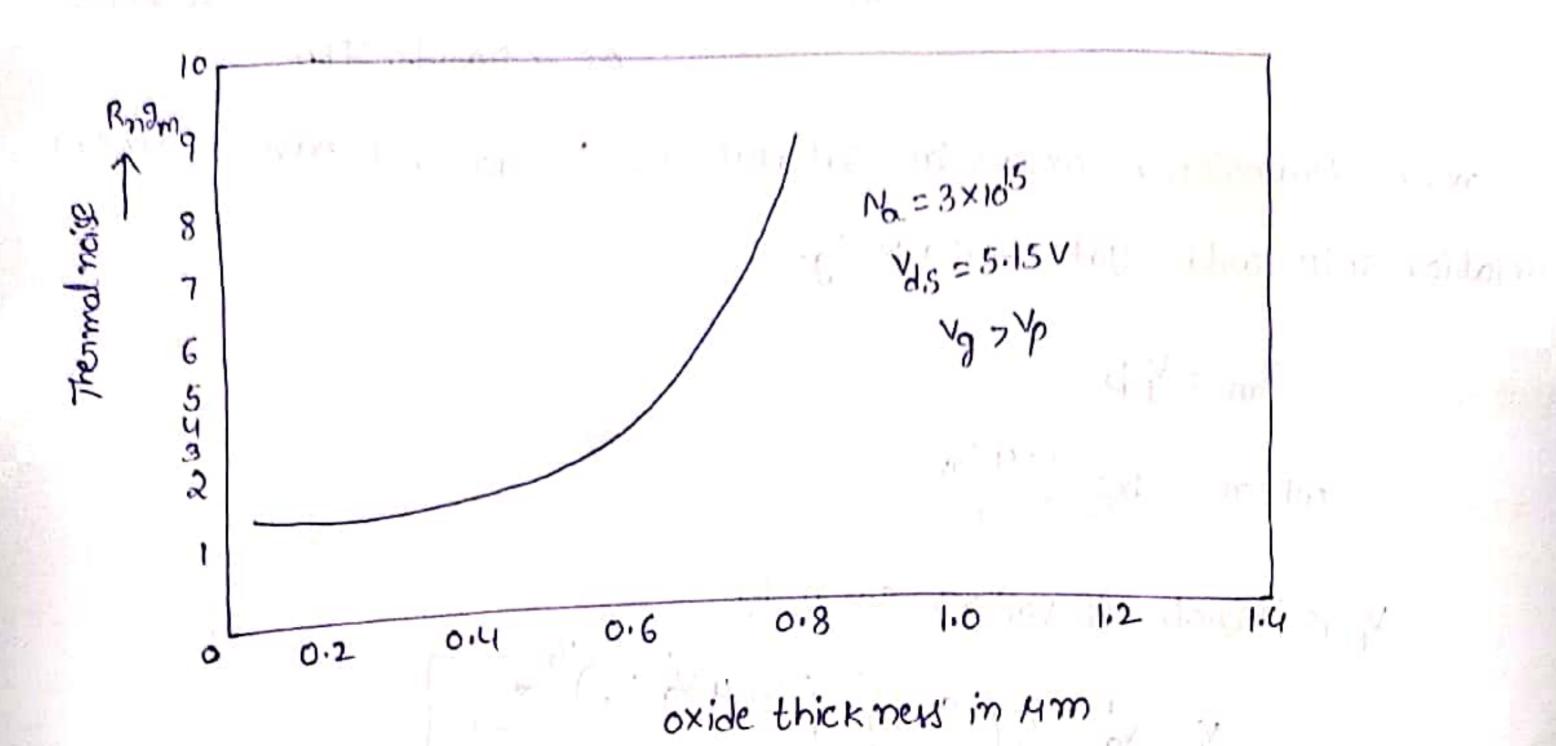

The subthreshold current I sub a cos- VE) W/KT

The transistor is in off state, then the Ygs-Ve is -ve and should be large as possible to minimize Isub.

with the scaling voltages,  $(v_{gs}-v_t)/kT$  reduces due to which subthreshold current Increases. To avoid this, both  $v_{gs}$  and  $v_t$  may be scaled along with  $v_{bo}$  by a larger factor. However, this causes electric field Strength to Increase and there by lower break down voltages.

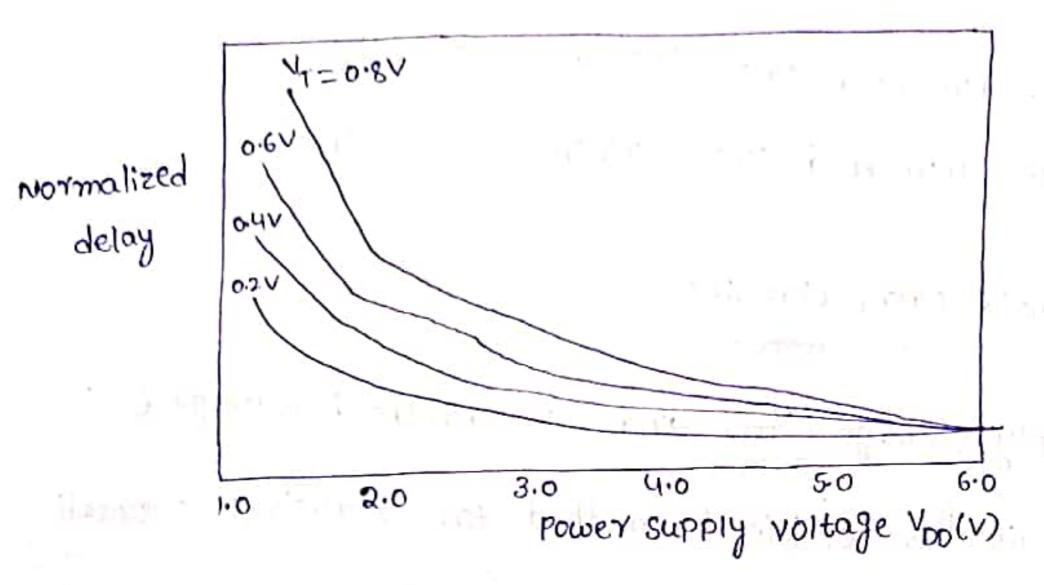

we derive that  $E_{max}$  is scaled by  $\alpha(\beta+m)/\beta(\ell+1)$ . Junction break down voltage BV is given by